# **MOSTEK 1981**

3870/F8 MICROCOMPUTER DATA BOOK

BEN SEGAL Field Applications Engineer 1762 Technology Dr./Suite 126 San Jose. CA 95110 Telephone (408) 287-5080/TWX: 910-338-2219

# 1981 3870/F8 MICROCOMPUTER DATA BOOK

Copyright © 1981 Mostek Corporation (All rights reserved)

Trade Marks Registered ®

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek.

The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

PRINTED IN USA February 1981 Publication Number MK79602

# 3870/F8 MICROCOMPUTER DATA BOOK

、

# **1981 MICROCOMPUTER DATA BOOK**

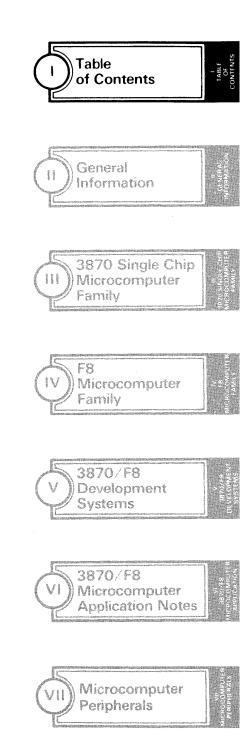

# TABLE OF CONTENTS

| I - Table of Contents                                       |         |

|-------------------------------------------------------------|---------|

| Functional Index                                            | I-i     |

|                                                             |         |

| II - General Information                                    |         |

| Order Information                                           |         |

| Package Descriptions                                        |         |

| Mostek Profile                                              |         |

| U.S. and Canadian Sales Offices                             |         |

| U.S. and Canadian Representatives                           |         |

| U.S. and Canadian Distributors                              |         |

| International Marketing Offices                             | II-xiii |

| III - 3870 Single Chip Microcomputer Family                 |         |

| 3870 Technical Manual                                       | -1      |

| Data Sheets                                                 |         |

| MK3870/38P70                                                | 111-77  |

| MK3873/38P73                                                |         |

| MK3875                                                      |         |

| MK38C70 and 38PC70                                          |         |

| MK14004 Display Terminal Controller DTC1                    |         |

| SCU1 Serial Control Unit                                    |         |

| SCU20 Serial Control Unit                                   |         |

| EPC1 EPROM Programming Controller                           |         |

| MK3870 Instruction Set                                      |         |

| SCU1 Operations Manual                                      |         |

|                                                             |         |

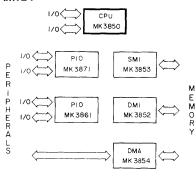

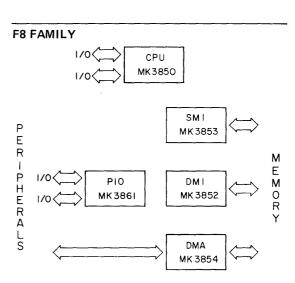

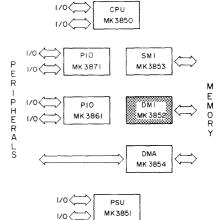

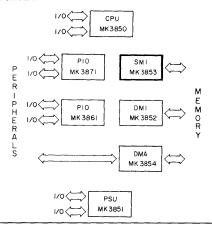

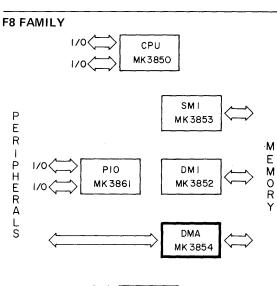

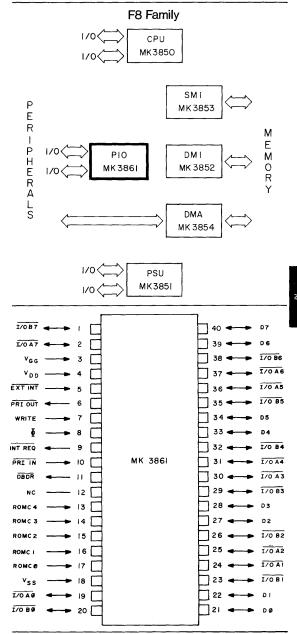

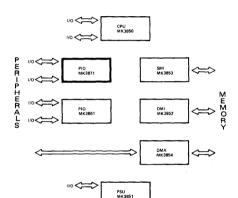

| IV - F8 Microcomputer Family                                |         |

| Data Sheets                                                 |         |

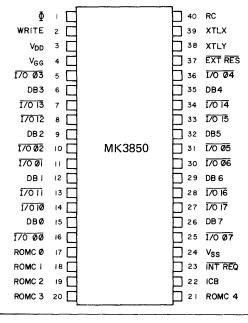

| MK3850 F8 Central Processing Unit.                          |         |

| MK3851 Program Storage Unit                                 |         |

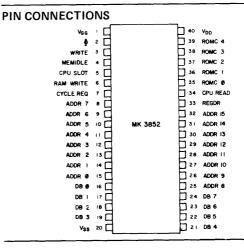

| MK3852 Dynamic Memory Interface                             |         |

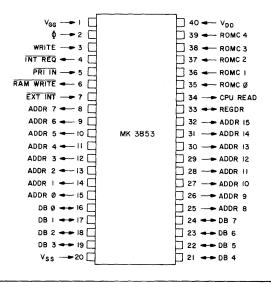

| MK3853 Static Memory Interface                              |         |

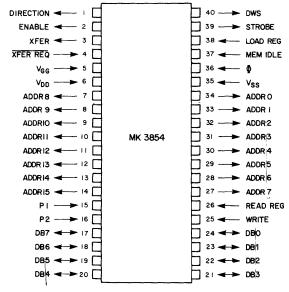

| MK3854 F8 Direct Memory Access                              |         |

| MK3861 Peripheral Input/Output                              |         |

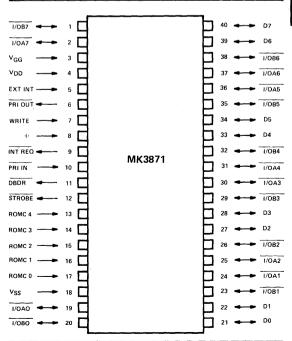

| MK3871 Peripheral Input/Output                              | 10-13   |

| V - 3870/F8 Development System Products                     |         |

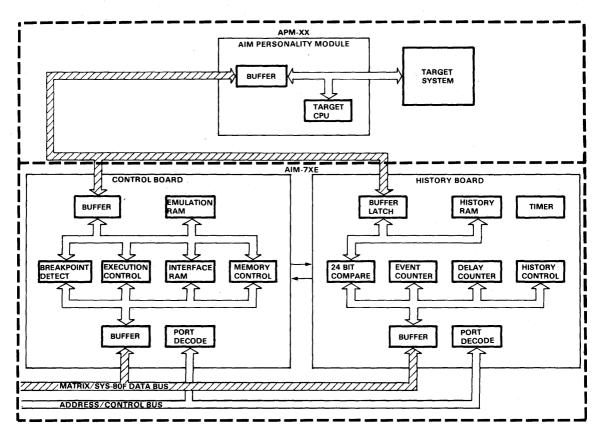

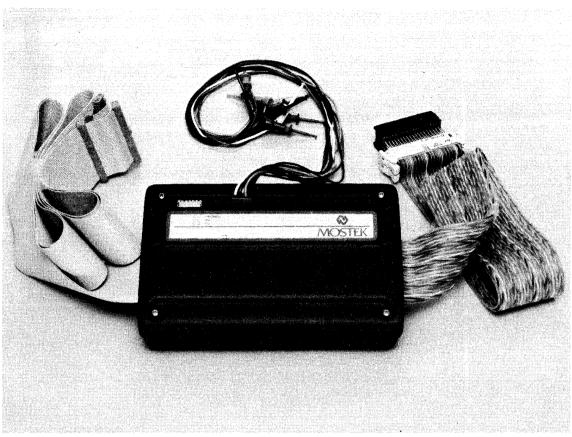

| AIM-7XE Application Interface Module                        |         |

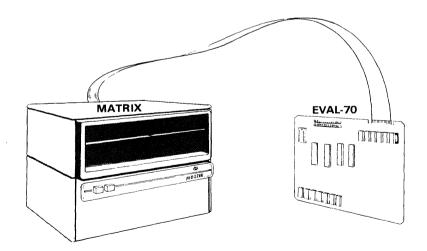

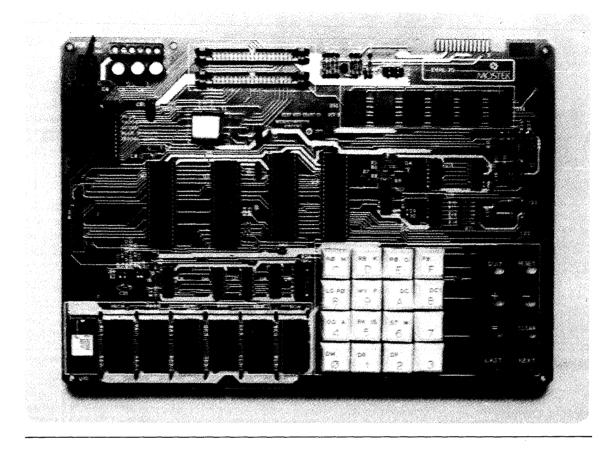

| EVAL-70 3870 Evaluation System                              |         |

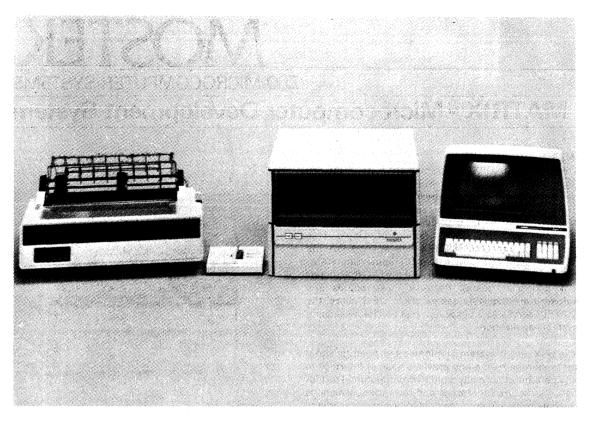

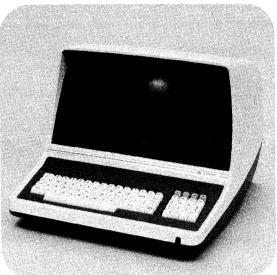

| MATRIX Matrix <sup>™</sup> Microcomputer Development System | V-11    |

| CRT                                                         | V-21    |

| LP Line Printer                                             | V-25    |

| PPG 8/16 Prom Programmer                                    |         |

| MK78157 Ansi Basic Software Interpreter                     | V-33    |

| MK78158 Fortran IV Compiler                                 | V-37    |

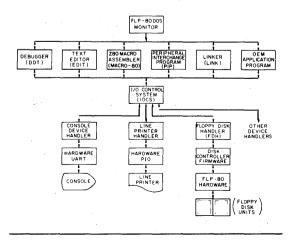

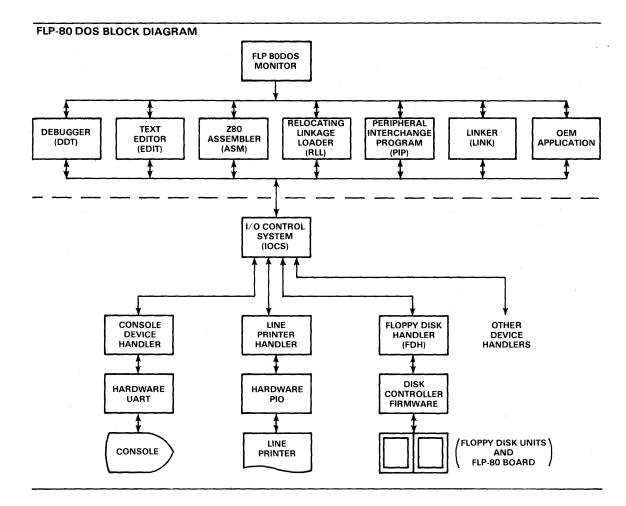

| MK78142, MK77962 FLP-80 DOS                                 | V-39    |

| XFOR-70 Fortran IV Cross Assembler                          | V-43    |

| MK79085 Macro 70                                            | V-45    |

# VI - 3870/F8 Microcomputer Application Notes

| Using the MK3873 Serial Port                                     | VI-1   |

|------------------------------------------------------------------|--------|

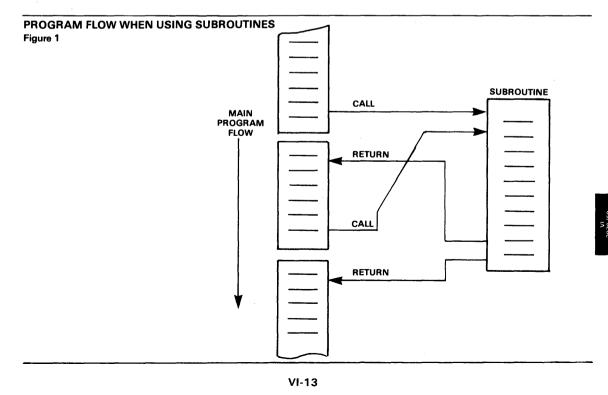

| Multilevel Subroutine Handling of F8 & 3870                      | VI-13  |

| Full Duplex Operation of the 3873 Serial Port                    | VI-23  |

| Controlling the MK3873 Serial Port                               | VI-51  |

| CRC Handling in the 3870 Family                                  | VI-81  |

| Expanding Mostek's F8 External Interrupt Capabilities            | VI-95  |

| Using Mostek's F8 in a Scanned Seven-Segment Display Application | VI-99  |

| Using Mostek's F8 in Scanned Keyboard Application                | VI-105 |

| Microcomputer Becomes Serial Control Unit                        | VI-113 |

| VFC Provides A/D Conversion For Single Chip Microcomputers       | VI-119 |

| Use of the MK3805 Clock RAM                                      | VI-125 |

| Using the MK3807 VCU in a Microprocessor Environment             | VI-183 |

# **VII - Microcomputer Peripherals**

| MK3807 Programmable CRT Video Control Unit                | . VII-1 |

|-----------------------------------------------------------|---------|

| MK3805 CMOS Microcomputer Clock RAM                       | VII-13  |

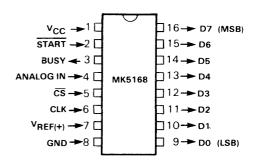

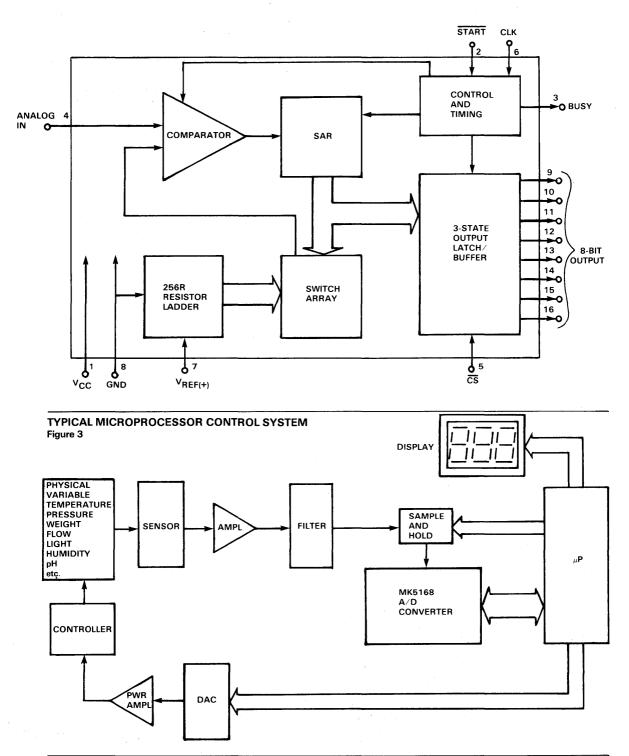

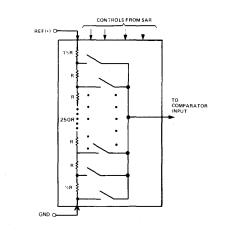

| MK5168(N) - 1 μP-Compatible A/D Converter                 | VII-21  |

| MK50808 8-Bit A/D Converter/8-channel Analog Multiplexer  | VII-29  |

| MK50816 8-Bit A/D Converter/16-Channel Analog Multiplexer | VII-37  |

.

# 3870/F8 MICROCOMPUTER DATA BOOK

· ·

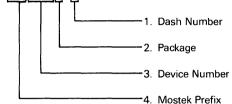

# ORDERING INFORMATION

Factory orders for parts described in this book should include a four-part number as explained below: Example: [MK[[3870][J]-[3]

### 1. Dash Number

One or two numerical characters defining specific device performance characteristic.

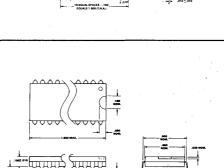

### 2. Package

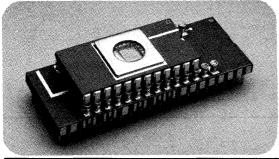

- P Gold side-brazed ceramic DIP

- J CER-DIP

- N Epoxy DIP (Plastic)

- R P-PROM

- K Tin side-brazed ceramic DIP

- T Ceramic DIP with transparent lid

- E Ceramic leadless chip carrier

- 3. Device number

| 1XXX or 1XXXX | - | Shift Register, ROM              |

|---------------|---|----------------------------------|

| 2XXX or 2XXXX | - | ROM, EPROM                       |

| 3XXX or 3XXXX | - | ROM, EPROM                       |

| 38XX          | - | Microcomputer Components         |

| 4XXX or 4XXXX | - | RAM                              |

| 5XXX or 5XXXX | - | Telecommunication and Industrial |

| 7XXX or 7XXXX | - | Microcomputer Systems            |

4. Mostek Prefix

**MK-Standard Prefix**

MKB-100% 883B screening, with final electrical test at low, room and high-rated temperatures.

II-ii

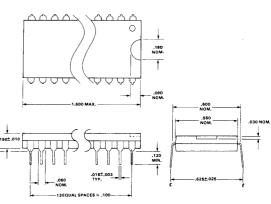

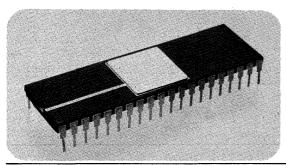

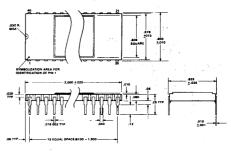

# **Package Descriptions**

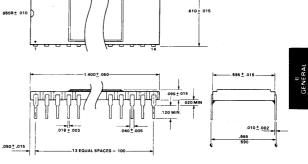

# Ceramic Dual-In-Line Package (P) 28 Pin

# Cerdip Hermetic Packaging (J) 28 Pin

.018 + .00

13 EQUAL SPACES AT . 100 EACH

# Plastic Dual-In-Line Package (N) 28 Pin

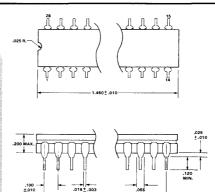

# Cerdip Hermetic Packaging (J) 40 Pin

حمصصم

ሌ ሌ

,814 2,010

80

NOTE: Overall length includes .005 flash on either end of package.

00000

00000)

ãoc

-----

II-iv

# Mostek - Technology For Today And Tomorrow

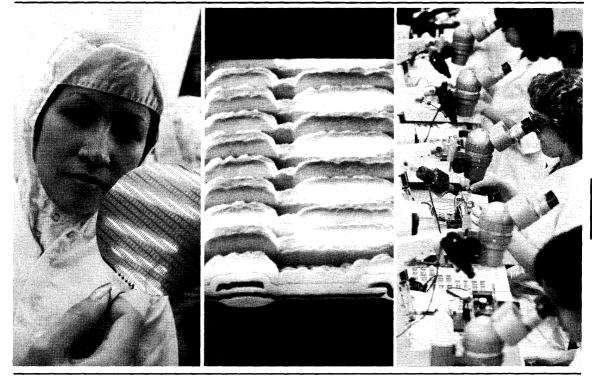

# TECHNOLOGY

From its beginning, Mostek has been an innovator. From the developments of the 1K dynamic RAM and the single-chip calculator in 1970 to the current 64K dynamic RAM, Mostek technological breakthroughs have proved the benefits and cost-effectiveness of metal oxide semiconductors. Today, Mostek represents one of the industry's most productive bases of MOS/LSI technology, including Direct-Step-on-Wafer processing and ion-implantation techniques.

The addition of the Microelectronics Research Center in Colorado Springs adds a new dimension to Mostek circuit design capabilities. Using the latest computer-aided design techniques, center engineers will be keeping ahead of the future with new technologies and processes.

# QUALITY

The worth of a product is measured by how well it is designed, manufactured and tested and by how well it works in your system.

In design, production and testing, the Mostek goal is meeting specifications the first time on every product. This goal requires strict discipline from the company and from its individual employees. Discipline, coupled with very personal pride, has enabled Mostek to build in quality at every level of production.

# **PRODUCTION CAPABILITY**

The commitment to increasing production capability has made Mostek the world's largest manufacturer of dynamic RAMs. We entered the telecommunications market in 1974 with a tone dialer, and have shipped millions of telecom circuits since then. More than two million of our MK3870 single-chip microprocessors are in use throughout the world. To meet the demand, production capability is being constantly increased. Recent construction in Dallas, Ireland and Colorado Springs has added some 50 percent to the Mostek manufacturing capacity.

### THE PRODUCTS

## **Telecommunications Products**

Mostek is the leading supplier of tone dialers, pulse dialers, and CODEC devices. As each new generation of telecommunications systems emerges, Mostek is ready with new generation components, including PCM filters, tone receivers, repertory dialers, new integrated tone dialers, and pulse dialers.

These products, many of them using CMOS technology, represent the most modern advancements in telecommunications component design.

# **Industrial Products**

Mostek's line of Industrial Products offers a high degree of versatility per device. This family of components includes various microprocessor-compatible A/D converters, a counter/time-base circuit for the division of clock signals, and combined counter/display decoders. As a result of the low parts count involved, an economical

alternative to discrete logic systems is provided.

### **Memory Products**

Through innovations in both circuit design, wafer processing and production, Mostek has become the industry's leading supplier of memory products.

An example of Mostek leadership is our new BYTEWYDE<sup>™</sup> family of static RAMs, ROMs, and EPROMs. All provide high performance, N words x 8-bit organization and common pin configurations to allow easy system upgrades in density and performance. Another important product area is fast static RAMs. With major advances in technology, Mostek static RAMs now feature access times as low as 55 nanoseconds. With high density ROMs and PROMs, static RAMs, dynamic RAMs and pseudostatic RAMs, Mostek now offers one of industry's broadest and most versatile memory product lines.

### **Microcomputer Components**

Mostek's microcomputer components are designed for a wide range of applications.

Our Z80 family is today's industry standard 8-bit microcomputer. The MK3870 family is one of the industry's most popular 8-bit single-chip microcomputers, offering upgrade options in ROM, RAM and I/O, all in the same socket. The 38P7X EPROM versions support and prototype the entire family.

# **Microcomputer Systems**

Complementing the component product line is the powerful MATRIX<sup>TM</sup> microcomputer development system, a Z80based, dual floppy-disk system that is used to develop and debug software and hardware for all Mostek microcomputers.

A software operating system, FLP-80DOS, speeds and eases the design cycle with powerful commands. BASIC, FORTRAN, and PASCAL are also available for use on the MATRIX.

Mostek's MD Series<sup>™</sup> features both stand-alone microcomputer boards and expandable microcomputer boards. The expandable boards are modularized by function, reducing system cost because the designer buys only the specific functional modules his system requires. All MDX boards are STD-Z80 BUS compatible.

### Memory Systems

Taking full advantage of our leadership in memory components technology, Mostek Memory Systems offers a broad line of products, all with the performance and reliability to match our industry-standard circuits. Mostek Memory Systems offers addin memory boards for popular DEC and Data General minicomputers.

Mostek also offers special purpose and custom memory boards for special applications.

A second s

II-viii

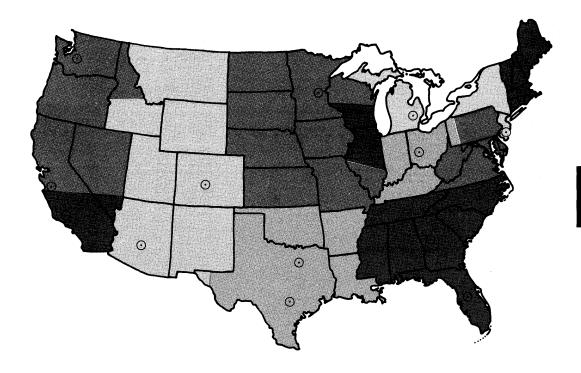

# **U.S. AND CANADIAN SALES OFFICES**

### CORPORATE HEADQUARTERS

Mostek Corporation 1215 W. Crosby Rd P. O. Box 169 Carrollton, Texas 75006

### **REGIONAL OFFICES**

Eastern U.S./Canada Assertin U.S./ Canada Mostek 49 W. Putnam, 3rd Floor Greenwich, Conn. 06830 203/622-0955 TWX 710-579-2928

# Northeast U.S. Mostek Mostek 29 Cummings Park, Suite #426 Woburn, Mass. 01801 617/935-0635 TWX 710-348-0459

Mid-Atlantic U.S.

Mostek East Gate Business Center East Gate Dusiness Center 125 Gaither Drive, Suite D Mt, Laurel, New Jersey 08054 609/235-4112 TWX 710-897-0723

### Southeast U.S.

Mostek Exchange Bank Bldg. 1111 N. Westshore Blvd. Suite 414 Tampa, Florida 33607 813/876-1304 TWX 810-876-4611

Atlanta Region 2 Exchange Place 2300 Peachford Rd. #2105 Atlanta, GA 30338 404/458-7922 TWX 810-757-4231

Upstate NY Region Mostek 4651 Crossroads Park Dr., Suite 201 Liverpool, NY 13088 315/457-2160

### Florida Region

Mostek 22521 Southwest 66th Ave. Apt. A211 Boca Raton, FL 33433

Chicago Region Mostek 701 E. irving Park Road Suite 206 Roselle, III. 60172 312/529-3993 TWX 910-291-1207

North Central U.S. Moet Mostek 6101 Green Valley Dr. Bloomington, Mn. 55438 612/831-2322 TWX 910-576-2802

South Central U.S.

South Central U.S. Mostek 3400 S. Dixie Ave. Suite 101 Kettering, Ohio 45439 513/299-3405 TWX 810-459-1625

Michigan Mostek Mostek Livonia Pavillion East 29200 Vassar, Suite 520 Livonia, Mich. 48152 313/478-1470 TWX 810-242-2978

Central U.S. Mostek 4100 McEwen Road Suite 151 Dallas, Texas 75234 214/386-9340

### Southwest Region

Mostek 4100 McEwen Road 4100 McEwen Road Suite 237 Dallas, Texas 75234 214/386-9141 TWX 910-860-5437

Chevy Chase #4 7715 Chevy Chase Dr., #116 Austin, TX 78752 512/458-5226 TWX 910-874-2007

Western Region Northern California Mostek

1762 Technology Drive Suite 126 San Jose, Calif. 95110

Seattle Region Mostek 1107 North East 45th St. Suite 411 Seattle, WA 98105 206/632-0245 TWX 910-444-4030

Southern California Southern California Mostek 18004 Skypark Blvd. Suite 140 Irvine, Calif. 92714 714/549-0397 TWX 910-595-2513

Arizona Region Arizona Region Mostek 2150 East Highland Ave. Suite 101 Suite 101 Phoenix, AZ 85016 602/954-6260 TWX 910-957-4581

Denver Region 3333 Quebec Street, #9090 Denver, CO 80207 303/321-6545 TWX 910-931-2583

# **U.S. AND CANADIAN REPRESENTATIVES**

ALABAMA Beacon Elect. Assoc., Inc. 11309 S. Memorial Pkwy. Suite G Huntsville, AL 35803 205/881-5031 TWX 810-726-2136

ARIZONA ARIZONA Summit Sales 7825 E. Redfield Rd. Scottsdale, AZ 85260 602/998-4850 TWX 910-950-1283

ARKANSAS AHRANSAS Beacon Elect. Assoc., Inc. P.O. Box 5382, Brady Station Little Rock, AK 72215 501/224-5449 TWX 910-722-7310

CALIFORNIA Harvey King, Inc. 8124 Miramar Road San Diego, CA 92126 714/566-5252 TWX 910-335-1231

COLORADO Waugaman Associates 4800 Van Gordon Wheat Ridge, C0 80033 303/423-1020 TWX 910-938-0750

CONNECTICUT New England Technical Sales 240 Pomeroy Ave. Meriden, CT 06450 203/237-8827 TWX 710-461-1126

FLORIDA FLORIDA Conley & Associates, Inc. P.O. Box 309 235 S. Central Oviedo, FL 32765 305/365-3283 TWX 810-856-3520

Conley & Associates, Inc. 4021 W. Waters Suite 2 Tampa, FL 33614 813/885-7658 TWX 810-876-9136

Conley & Associates, Inc. P.O. Box 700 1612 N.W. 2nd Avenue Boca Raton, FL 33432 305/395-6108 TWX 510-953-7548

GEORGIA Conley & Associates, Inc. 3951 Pleasantdale Road Suite 201 Suite 201 Doraville, GA 30340 404/447-6992 TWX 810-766-0488

ILLINOIS Carlson Electronic Sales\* 600 East Higgins Road Elk Grove Village, IL 60007 312/956-8240 TWX 910-222-1819

INDIANA Rich Electronic Marketing\* 599 Industrial Drive Carmel, IN 46032 317/844-8462 TWX 810-260-2631

Rich Electronic Marketing 3448 West Taylor St. Fort Wayne, IN 46804 219/672-3329 TWX 810-332-1404

tOWA Cahill, Schmitz & Cahill, Inc. 208 Collins Rd. N.E. Suite K Cedar Rapids, IA 52402 319/377-8219 TWX 910-525-1363

Carlson Electronic Sales 204 Collins Rd. NE Cedar Rapids, IA 52402 319/377-6341 TWX 910-222-1819

KANSAS Rush & West Associates\* 107 N. Chester Street Olathe, KN 66061 913/764-2700 TWX 910-749-6404

KENTUCKY Rich Electronic Marketing 5910 Bardstown Road P. O. Box 91147 Louisville, KY 40291 502/239-2747 TWX 810-535-3757

MARYLAND Arbotek Associates 3600 St. Johns Lane Ellicott City, MD 21043 301/461-1323 TWX 710-862-1874

MASSACHUSETTS New England Technical Sales\* 135 Cambridge Street Burlington, MA 01803 617/272-0434 TWX 710-332-0435

MICHIGAN Action Components 19547 Coachwood Rd. Riverview, MI 48192 313/479-1242

MINNESOTA Cahill, Schmitz & Cahill, Inc. 315 N. Pierce St. Paul, MN 55104 612/646-7217 TWX 910-563-3737

MISSOUDI Rush & West Associates 481 Melanie Meadows Lane Ballwin, MO 63011 314/394-7271

NORTH CAROLINA NORTH CAROLINA Conley & Associates, Inc. 3301 Womans Club Drive Suite 130 Raleigh, NC 27616 919/787-8090 TWX 510-928-1829

# NEW JERSEY Tritek Sales, Inc. 21 E. Euclid Ave. Haddonfield, NJ 08033 609/429-1551 005/429-1551 215/627-0149 (Philadelphia Line) TWX 710-896-0881

NEW MEXICO Waugaman Associates P.O. Box 14894 Albuquerque, NM 87111

Albuquerque, NM 8/111 or 9004 Menaul NE Suite 7 Albuquerque, NM 87112 505/294-1437 505/294-1436 (Ans. Service)

NEW YORK NEW YOHK ERA Inc. 354 Veterans Memorial Highway Commack, NY 11725 516/543-0510 TWX 510-226-1485 (New Jersey Phone # 800/645-5500, 5501)

Precision Sales Corp. 5 Arbustus Ln., MR-97 Binghamton, NY 13901 607/648-3686

Precision Sales Corp.\* 1 Commerce Blvd. Liverpool, NY 13088 315/451-3480 TWX 710-545-0250

Precision Sales Corp. 3594 Monroe Avenue Pittsford, NY 14534 716/381-2820

Precision Sales Corp. Drake Road Pleasant Valley, NY 12569 914/635-3233

оню Rich Electronic Marketing 7221 Taylorsville Road Dayton, Ohio 45424 513/237-9422 TWX 810-459-1767

Rich Electronic Marketing 141 E. Aurora Road Northfield, Ohio 44067 216/468-0583 TWX 810-427-9210

OREGON

Northwest Marketing Assoc. 9999 S.W. Wilshire St. Suite 124 Portland OR 97225 503/297-2581 TELEX 36-0465 (AMAPORT PTL) TEXAS

Southern States Marketing, Inc. P.O. Box 8000 Addison, TX 75001 214/387-2489 TWX 910-860-5138

Southern States Marketing, Inc. 7745 Chevy Chase Suite 219 Austin, TX 78752 512/452-9459

Southern States Marketing, Inc. 9730 Town Park Drive, Suite 104 Houston, Texas 77036 713/988-0991 TWX 910-881-1630

UTAH UTAH Waugaman Associates 2520 S. State Street #224 Salt Lake City, UT 84115 801/467-4263 TWX 910-925-4073

WASHINGTON Northwest Marketing Assoc. 12835 Bellevue-Redmond Rd. Suite 203E Bellevue, WA 98005 206/455-5846 TWX 910-443-2445

WISCONSIN Carlson Electronic Sales Northbrook Executive Ctr. 10701 West North Ave. Suite 209 Milwaukee, WI 53226 414/476-2790 TWX 910-222-1819

CANADA Cantec Representatives Inc.\* 1573 Laperriere Ave. Ottawa, Ontario Canada K1Z 7T3 613/725-3704 TWX 610-562-8967

Cantec Representatives Inc. 83 Galaxy Blvd., Unit 1A (Rexdale) Toronto, Canada M9W 5X6 416/675-2460 TWX 610-492-2655

Cantec Representatives Inc. 15737 rue Pierrefonds St. Ste-Genevieve, P. Q. (Montreal) H9H 1G3 514/620-6313 TWX 610-422-3985

# **U.S. AND CANADIAN DISTRIBUTORS**

ARIZONA Kierulff Electronics 4134 E. Wood St. Phoenix, AZ 85040 602/243-4101 TWX 910/951-1550 Wyle Distribution Group 8155 North 24th Avenue Phoenix, Arizona 85021 602/249-2232 TWX 910/951-4282

### CALIFORNIA

Bell Industries 1161 N. Fair Oaks Avenue Sunnyvale, CA 94086 408/734-8570 TWX 910/339-9378 Arrow Electronics 521 Weddell Dr. Sunnyvale, CA 94086 408/745-6600 TWX 910/339-9371 Kierulff Electronics 2585 Commerce Way Los Angeles, CA 90040 213/725-0325 TWX 910/580-3106 Kierulff Electronics 8797 Balboa Avenue San Diego, CA 92123 714/278-2112 TWX 910/335-1182 Kierulff Electronics 14101 Franklin Avenue Tustin CA 92680 714/731-5711 TWX 910/595-2599 Schweber Electronics 17811 Gillette Avenue Irvine, CA 92714 714/556-3880 TWX 910/595-1720 Wyle Distribution Group 124 Maryland Street El Segundo, CA 90245 213/322-8100 TWX 910/348-7111 Wyle Distribution Group 9525 Chesapeake Drive San Diego, CA 92123 714/565-9171 TWX 910/335-1590 Wyle Distribution Group 17872 Cowan Ave. Irvine, CA 92714 714/641-1600 TWX 910/348-7111 Wyle Distribution Group 3000 Bowers Ave. Santa Clara, CA 95051 408/727-2500 TWX 910/338-0296

### COLORADO

Kierulff Electronics 10890 E. 47th Avenue Denver, CO 80239 303/371-6500 TWX 910/932-0169 Wyle Distribution Group 451 E. 124th Ave. 451 E. 124th Ave. Thornton, CO 80241 303/457-9953 TWX 910/936-0770

### CONNECTICUT

Arrow Electronics 12 Beaumont Rd. Wallingford, CT 06492 203/265-7741 TWX 710/476-0162 Schweber Electronics Schweber Electronics Finance Drive Commerce Industrial Park Danbury, CT 06810 203/792-3500 TWX 710/456-9405

FLORIDA Arrow Electronics 1001 N.W. 62nd St. Suite 108 Suite 108 Ft. Lauderdale, FL 33309 305/776-7790 TWX 510/955-9456 Arrow Electronics 115 Palm Bay Road, N.W. Suite 10 Bidg. 200 Palm Bay, FL 32905 305/725-1480 TWX 510/959-6337 Diplomat Southland 2120 Calumet Clearwater, FL 33515 813/443-4514 TWX 810/866-0436 Kierulff Electronics 2047 Let Davis Kierulff Electronics 3247 Tech Drive St. Petersburg, FL 33702 813/576-1966 TWX 810/863-5625

GEORGIA Arrow Electronics 2979 Pacific Ave. Norcross, GA 30071 404/449-8252 TWX 810/766-0439 Schweber Electronics 4126 Pleasantdale Road Atlanta, GA 30340 404/449-9170

### ILLINOIS

Arrow Electronics 492 Lunt Avenue P. O. Box 94248 Schaumburg, IL 60193 312/893-9420 TWX 910/291-3544 Bell Industries 3422 W. Touhy Avenue Chicago, IL 60645 312/982-9210 TWX 910/223-4519 Kierulff Electronics 1536 Lanmeier Elk Grove Village, IL 60007 312/640-0200 TWX 910/222-0351

INDIANA Advent Electronics 8446 Moller Indianapolis, IN 46268 317/297-4910 TWX 810/341-3228 Ft. Wayne Electronics 3606 E. Maumee Tk. Wayne, IN 46803 219/423-3422 TWX 810/332-1562 Pioneer/Indiana 6408 Castleplace Drive Indianapolis, IN 46250 317/849-7300 TWX 810/260-1794

IOWA IOWA Advent Electronics 682 58th Avenue Court South West Cedar Rapids, IA 52404 319/363-0221 TWX 910/525-1337

MASSACHUSETTES Kierulff Electronics 13 Fortune Drive Billerica, MA 01821 617/935-5134 TWX 710/390-1449 Lionex Corporation 1 North Avenue Burlington, MA 01803 617/272-9400 TWX 710/332-1387 Schweber Electronics 25 Wiggins Avenue Bedford, MA 01730 617/275-5100 TWX 710/326-0268 Arrow Electronics 96D Commerce Way Woburn, MA 01801 617/933-8130 TWX 710/393-6770

MARYLAND Arrow Electronics 4801 Benson Avenue Baltimore, MD 21227 301/247-5200 TWX 710/236-9005 Schweber Electronics 9218 Gaither Rd 9218 Gaither Rd. Gaithersburg, MD 20760 301/840-5900 TWX 710/828-9749

### MICHIGAN

Arrow Electronics 3810 Varsity Drive Ann Arbor, MI 48104 313/971-8220 TWX 810/223-6020 Schweber Electronics 33540 Schoolcraft Road Livonia, MI 48150 313/525-8100 TWX 810/242-2983

MINNESOTA Arrow Electronics 5251 W. 73rd Street Edina, MN 55435 612/830-1800 TWX 910/576-3125 Industrial Components 5229 Edina Industrial Blvd. Minneapolis, MN 55435 612/831-2666 TWX 910/576-3153

# MISSOURI Missouri Olive Electronics 9910 Page Blvd. St. Louis, MO 63132 314/426-4500 TWX 910/763-0720

Semiconductor Spec 3805 N. Oak Trafficv Kansas City, MO 64116 816/452-3900 TWX 910/771-2114

NEW HAMPSHIRE Arrow Electronics 1 Perimeter Rd. Manchester, NH 03103 603/668-6968 TWX 710/220-1684

NEW JERSEY NEW JERSEY Arrow Electronics Pleasant Valley Avenue Morrestown, NJ 08057 609/235-1900 TWX 710/897-0829 Arrow Electronics 285 Midland Avenue Saddlebrook, NJ 07662 201/797-5800 TWX 710/988-2206 Kierulff Electronics 3 Edison Place Fairfield, NJ 07006 201/575-6750 TWX 710/734-4372 Schweber Electronics 18 Madison Road Fairfield, NJ 07006 201/227-7880 TWX 710/734-4305

# **U.S. AND CANADIAN DISTRIBUTORS**

NEW MEXICO Bell Industries 11728 Linn N.E. Albuquerque, NM 87123 505/292.2700 TWX 910/989-0625 Arrow Electronics 2460 Alamo Ave. S.E. Albuquerque, NM 87106 505/243-4566 TWX 910/989-1679

### NEW YORK

Arrow Electronics 900 Broad Hollow Rd. Farmingdale, L.I., NY 11735 516/694-6800 TWX 510/224-6494 TWX 510/224-6494 Arrow Electronics 7705 Maltlage Drive P. O. Box 370 Liverpool, NY 13088 315/652-1000 TWX 710/545-0230 Arrow Electronics 3000 S. Winton Road Rochester, NY 14623 716/275-0300 TWX 510/253-4766 Arrow Electronics 20 Oser Ave. Hauppauge, NY 11787 516/231-1000 TWX 510/227-6623 Lionex Corporation 400 Oser Ave. Hauppauge, NY 11787 516/273-1660 TWX 510/221-2196 Schweber Electronics 2 Twin Line Circle Rochester, NY 14623 716/424-2222 Schweber Electronics Jericho Turnpike Westbury, NY 11590 516/334-7474 TWX 510/222-3660

# NORTH CAROLINA Arrow Electronics 938 Burke St. Winston Salem, NC 27102

919/725-8711 TWX 510/931-3169 Hammond Electronics 2923 Pacific Avenue Greensboro, NC 27406 919/275-6391 TWX 510/925-1094

оню Arrow Electronics Arrow Electronics 7620 McEwen Road Centerville, OH 45459 513/435-5563 TWX 810/459-1611 Arrow Electronics 10 Knoll Crest Drive Reading, OH 45237 513/761-5432 TWX 810/461-2670 Arrow Electronics 6238 Cochran Road Solon, OH 44139 216/248-3990 TWX 810/427-9409 TWX 810/427-9409 Schweber Electronics 23880 Commerce Park Road Beachwood, OH 44122 216/464-2970 TWX 810/427-9441 Pioneer/Cleveland 4800 East 131st Street Cleveland, OH 44105 215/587-3600 TWX 810/422-2211 Pioneer/Dayton-Industrial 4433 Interpoint Blvd. Dayton, OH 45424 513/236-9900 TWX 810/459-1622

### OREGON

Kierulff Electronics 14273 NW Science Park Portland, OR 97229 503/641-9150 TWX 910/467-8753

PENNSYLVANIA Schweber Electronics 101 Rock Road Horsham, PA 19044 215/441-0600 Arrow Electronics 650 Seco Rd. Monroeville, PA 15146 412/856-7000 412/856-7000 Pioneer/Pittsburgh 560 Alpha Drive Pittsburgh, PA 15238 412/782-2300 TWX 710/795-3122

# SOUTH CAROLINA Hammond Electronics 1035 Lown Des Hill Rd. Greenville, SC 29602 803/233-4121 TWX 810/281-2233

TEXAS Arrow Electronics 13715 Gamma Road P.O. Box 401068 Dallas, TX 75240 214/386-7500 TWX 910/860-5377 Quality Components 10201 McKalla Suite D Austin, TX 78758 512/835-0220 TWX 910/874-1377 Quality Components 4257 Kellway Circle Addison, TX 75001 214/387-4949 TWX 910/860-5459 Quality Components 6126 Westline Houston, TX 77036 713/772-7100 Schweber Electronics 7420 Harwin Drive Houston, TX 77036 713/784-3600 TWX 910/881-1109

TEXAS

### UTAH

Bell Industries 3639 W. 2150 South Salt Lake City, UT 84120 801/972-6969 TWX 910/925-5686 2121 South 3600 West Salt Lake City, UT 84104 801/973-6913

WASHINGTON Kierulff Electronics 1005 Andover Park East Tukwita, WA 98188 206/575-4420 TWX 910/444-2034 Wyle Distribution Group 1750 132nd Avenue N.E. Bellevue, Washington 98005 206/453-8300 TWX 910/443-2526

WISCONSIN Arrow Electronics 434 Rawson Avenue Oak Creek, WI 53154 414/764-6600 TWX 910/262-1193 Kierulff Electronics 2212 E. Moreland Blvd. Waukesha, WI 53186 414/784-8160 TWX 910/262-3653

CANADA Prelco Electronics 2767 Thames Gate Drive Mississauga, Ontario Toronto L4T 1G5 416/678-0401 TWX 610/492-8974 Prelco Electronics 480 Port Royal St. W. Montreal 357 P.O. H3L 2B9 514/389-8051 TWX 610/421-3616 Preico Electronics 1770 Woodward Drive Ottowa, Ontario K2C 0P8 613/226-3491 Telex 05-34301 R.A.E. Industrial 3455 Gardner Court Burnaby, B.C. V5G 4J7 604/291-8866 TWX 610/929-3065 Zentronics 141 Catherine Street Ottawa, Ontario K2P 1C3 613/238-6411 Telex 05-33636 Zentronics 1355 Meyerside Drive Mississauga, Ontario (Toronto) L5T 1C9 416/676-9000 Telex 06-983657 Zentronics 5010 Rue Pare Montreal, Quebec M4P 1P3 514/735-5361 Telex 05-827535 Zentronics 590 Berry Street St. James, Manitoba (Winnipeg) R2H OR4 204/775-8661 Zentronics 480A Dutton Drive Waterloo, Ontario N2L 4C6 519/884-5700

# INTERNATIONAL MARKETING OFFICES

### EUROPEAN HEAD OFFICE Mostek International Av de Tervuren 270-272 B-1150 Brussels/Belgium 02/762 18.80 Telex: 62011

### FRANCE

Mostek France s.a.r.l. 30 Rue du Morvan SILIC 505 F-94623 Rungis Cedex (1) 687 34.14 Telex: 204049

### GERMANY PLZ 1-5 Mostek GmbH FriedlandstraBe D-2085 Quickborn (4106) 2077/78 Telex: 213685

PLZ 6-7 Mostek GmbH SchurwaldstraBe 15 D-7303 Neuhausen/Filder 7158/66.45 Telex: 72.38.86

### PLZ 8 Mostek GmbH Zaunkonigstr. 18 D-8021 Ottobrunn 089-609 1017 Telex: 5216516

### ITALY Mostek Italia SRL Via G.D. Guerrazzi 27 I 20145 Milano (02) 318.5337/349.2696 and 34.23.98 Telex: 333601

JAPAN Mostek Japan KK Sanyo Bldg 3F 1-2-7 Kita-Aoyama Minato-Ku, Tokyo 107 (03) 404-7261 Telex: J23686

### SWEDEN Mostek Scandinavia AB Magnusvagen 1/8 tr S-1731 Jarfalla 0758-343 38/343 48 Telex: 12997

### UNITED KINGDOM Mostek U.K. Ltd.

Masons House, 1-3 Valley Drive Kingsbury Road London, N.W.9 01-204 9322 Telex: 25940

# INTERNATIONAL SALES REPRESENTATIVES/DISTRIBUTORS

### AUSTRIA

Transistor Vertriebsges, mbH AuhofstraBe 41 A A-1130 Vienna (0222) 82 9451, 82 9404 Telex: 01-3738

### BELGIUM

Sotronic 14 Rue Pere De Deken B-1040 Brussels 02 736.10.07. Telex: 25141

DENMARK Semicap APS Gammel Kongevej 148 DK-1850 Copenhagen 01-22.15.10 Telex: 15987

### FINLAND S.W. Instruments Karstulantie 4B SF-00550 Helsinki 55 8-0-73.82.65 Telex: 122411

FRANCE Societe Copel Rue Fourny, Z.I. B.P. 22, F-78 530 BUC (1)-735.33.20 Telex: 204 534

P.E.P. 4 Rue Barthelemy F-92120 Montrouge (1)-735.33.20 Telex: 204 534

SCAIB 80 Rue d'Arcueil SILIC 137 F-94150 Rungis Cedex (1) 687.23.12 Telex: 204674

Sorhodis 150-152 Rue A. France F69100 Villeurbanne (78) 850044 Telex: 380181 GERMANY Dr Dohrenberg Bayreuther StraBe 3 D-1000 Berlin 30 030-213.80.43 Telex: 0 184860

Neye Enatechnik GmbH SchillerstraBe 14 D-2085 Quickborn 04106-612-1 Telex: 0 213.590

Branch offices in: Berlin, Hannover, Dusseldorf, Darmstadt, Stuttgart, Munchen.

Raffel-Electronic GmbH LochnerstraBe 1 D-4030 Ratingen 1 0 2102-280.24 Telex: 8585180

Siegfried Ecker Koenigsberger StraBe 2 D-6120 Michelstadt 0 6061-2233 Telex: 4191630

Matronic GmbH Lichtenberger Weg 3 D-7400 Tubingen 07071-24331 Telex: 7262879

Dema-Electronic GmbH BlutenstraBe 21 D-8000 Munchen 40 (089) 288018/19 Telex: 05-29345

ITALY Comprel s.r.l. V.le Romagna. 1 I-20092 Cinisello B. (MI) (02) 61.20.641/2/3/4/5 Telex: 332484

Emesa S.P.A. Via L. da Viadana, 9 I-20122 Milano (02) 869.0616 Telex: 335066

Branch offices in Bologna, Firenze, Lavagna, Loreto, Padova, Roma, Torino THE NETHERLANDS Nijkerk Elektronika BV Drentestraat 7 1083 HK Amsterdam (020) 428. 933 Telex: 11625

SWEDEN Interelko AB Strandbergsgatan, 47 S-12221 Enskede 081 132 160 Telex: 10 689

Lagercrantz Elektronik AB Box M48 Kanalvagens S-19421 Upplands Vasby 0760 861 20 Telex: 11275

SPAIN Comelta S.A. CiaElectronica Tecnicas Aplicadas Diputacion, 79 Entlo 1-2 Barcelona-15 325 70 62 325 75 54 Telex: 519 34

Comelta S.A. Emilio Munoz 41, ESC 1 Planta 1 Nave 2 Madrid-17 01-754 3001/3077 Telex: 42007

SWITZERLAND Memotec AG CH-4932 Lotzwil 063-28.11.22 Telex: 68636

NORWAY Hefro Tekniska A/S Postboks 6596 Rođelkka Oslo 5 02-38.02.86 Telex: 16205 PORTUGAL Digicontrole LDA Rua Tenente Ferreira Durao 33 R/C 1300 Lisboa 19-688442/652613 Telex: 13639

UNITED KINGDOM Celdis Limited 37-39 Loverock Road Reading Berks. RG 31 ED

0734-58.51.71 Telex: 848370

Neville Street Chadderton Oldham Lancashire OL9 6LF 061-652.04.31 Telex: 669971

Pronto Electronic Systems Ltd, 466-478 Cranbrook Road Gants Hill IIIford Essex 1G2 6LE 01-544 6222 Telex: 895 4213

VSI Electronics (UK) Ltd. Roydondury Industrial Park Horsecroft Rd. Harlow Essex CM19 5BY (0279) 35477 Telex: 81387

YUGOSLAVIA Chemcolor Inozemma Zastupstva Proleterskih brigada 37-a 41001 Zagreb 041-513.911 Telex: 21236

Branch office in Beograd

### ISRAEL

Telsys Ltd. 12, Kehilat Venetsia St. Tel Aviv. Israel 482126/7/8 Telex: 032392

For all other countries MOSTEK INTERNATIONAL Av de Tervuren 270-272 B-1150 Brussels/Belgium 02/762 18.80 Telex: 62011 or

MOSTEK CORPORATION International Dept. 1215 West Crosby Road, Carrollton, Texas 75006, USA 214/323 6000 Telex: 730423 -

# 3870/F8 MICROCOMPUTER DATA BOOK

# **Technical Manual**

# MK3870 FAMILY

111-2

.

# TABLE OF CONTENTS

| SEC | TION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PAGE                                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 111-7                                                                                                                                                                |

| 2.0 | PART IDENTIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111-9                                                                                                                                                                |

| 3.0 | FUNCTIONAL PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 111-13                                                                                                                                                             |

| 4.0 | MK3870 ARCHITECTURE         4.1       INTRODUCTION         4.2       MAIN CONTROL LOGIC         4.3       ARITHMETIC AND LOGIC UNIT (ALU)         4.4       ACCUMULATOR (A)         4.5       THE STATUS REGISTER (W)         4.5.1       SIGN (S BIT)         4.5.2       CARRY (C BIT)         4.5.3       ZERO (Z BIT)         4.5.4       OVERFLOW (O BIT)         4.5.5       INTERRUPTS (ICB BIT)         4.6       MAIN MEMORY AND MAIN MEMORY ADDRESSING         4.7       SCRATCHPAD and IS         4.8       I/O PORTS         4.9       EXTERNAL RESET         4.10       SERIAL I/O         4.11       STANDBY POWER | . III-15<br>. III-15<br>. III-16<br>. III-16<br>. III-16<br>. III-16<br>. III-17<br>. III-17<br>. III-17<br>. III-17<br>. III-19<br>. III-20<br>. III-20<br>. III-21 |

| 5.0 | TIMER AND EXTERNAL INTERRUPT OPERATION5.1INTRODUCTION5.2INTERRUPT CONTROL PORT5.3INTERVAL TIMER MODE5.4PULSE WIDTH MEASUREMENT MODE5.5EVENT COUNTER MODE5.6EXTERNAL INTERRUPTS5.7INTERRUPT HANDLING                                                                                                                                                                                                                                                                                                                                                                                                                              | . 111-25<br>. 111-25<br>. 111-26<br>. 111-29<br>. 111-30<br>. 111-30                                                                                                 |

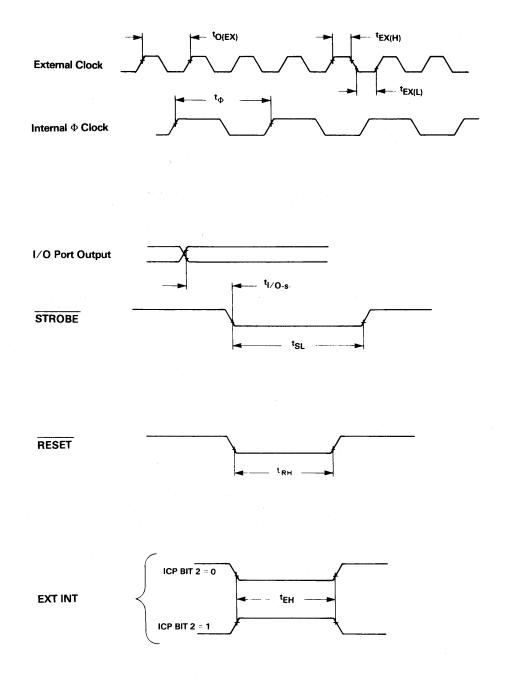

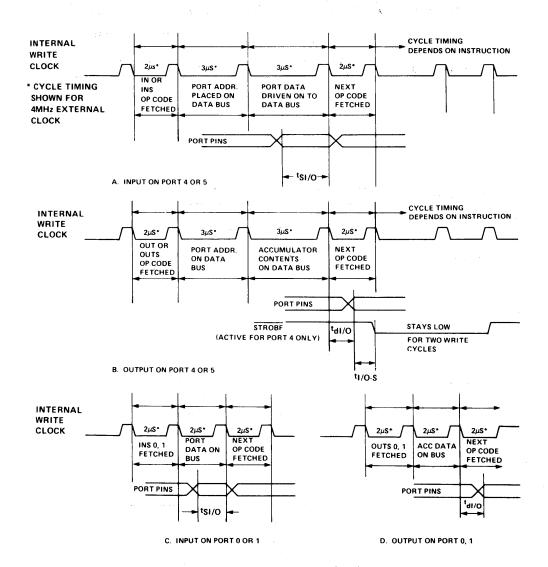

| 6.0 | TIMING         6.1       TIMING SIGNALS         6.2       INSTRUCTION EXECUTION         6.3       MAIN MEMORY ACCESS CYCLE         6.4       I/O PORT ACCESS CYCLE         6.5       INTERRUPT TIMING         6.6       SUMMARY OF INTERRUPT SEQUENCE         6.7       EXTERNAL INTERRUPT TIMING         6.8       RESET TIMING         6.9       TIMER ERRORS                                                                                                                                                                                                                                                                  | . 111-33<br>. 111-33<br>. 111-34<br>. 111-35<br>. 111-35<br>. 111-37<br>. 111-38<br>. 111-38<br>. 111-38                                                             |

# TABLE OF CONTENTS

SECTION

PAGE

| 7.0 | ) мк  | 3870 HA | ARDWARE IMPLEMENTATION III-41           |

|-----|-------|---------|-----------------------------------------|

|     | 7.1   | INTRO   | DUCTION III-41                          |

|     | 7.2   | POWE    | R-ON-CLEAR III-41                       |

|     | 7.3   | VCC D   | ECOUPLING III-43                        |

|     | 7.4   | TEST L  | _OGIC III-44                            |

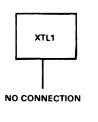

|     | 7.5   | 3870    | TIME BASE OPTIONS III-44                |

|     |       | 7.5.1   | CRYSTAL SELECTION III-44                |

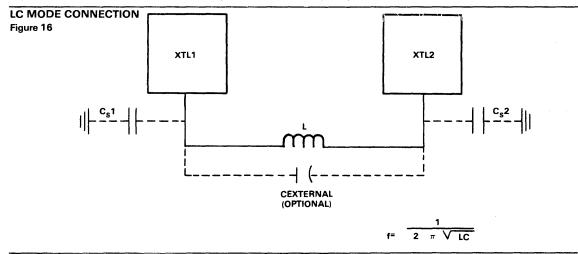

|     |       | 7.5.2   | LC NETWORK III-45                       |

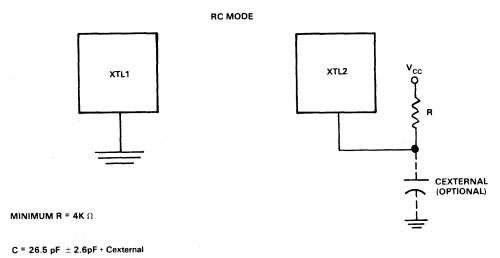

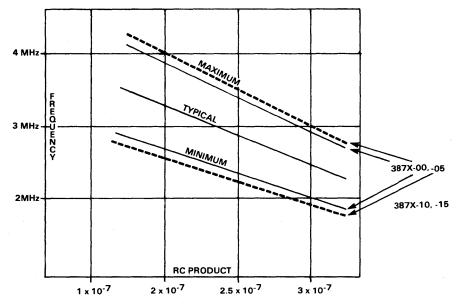

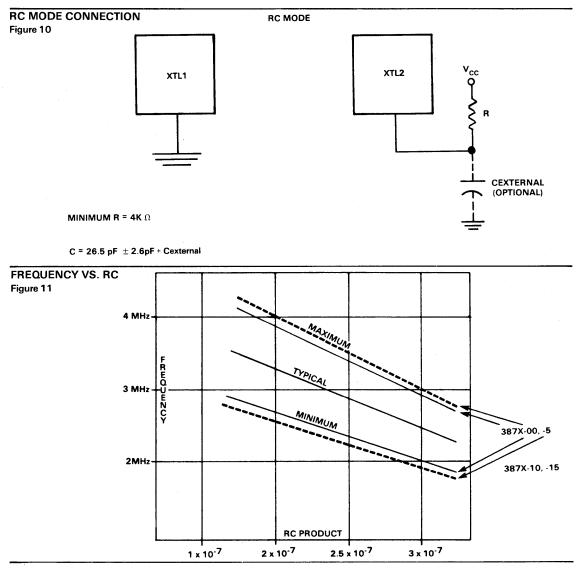

|     |       | 7.5.3   | RC CLOCK CONFIGURATION III-45           |

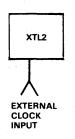

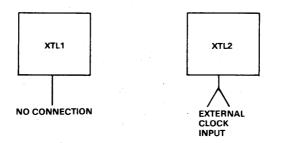

|     |       | 7.5.4   | EXTERNAL CLOCK CONFIGURATION III-46     |

| 8.0 | ) мк: | 3870 IN | STRUCTION SET                           |

|     | 8.1   |         | DUCTION                                 |

|     | 8.2   | 3870    | ADDRESSING MODES III-47                 |

|     |       | 8.2.1   | IMMEDIATE ADDRESSING III-47             |

|     |       | 8.2.2   | IMPLIED ADDRESSING III-47               |

|     |       | 8.2.3   | RELATIVE ADDRESSING III-47              |

|     |       | 8.2.4   | EXTENDED ADDRESSING III-48              |

|     |       | 8.2.5   | SCRATCHPAD ADDRESSING III-48            |

|     |       | 8.2.6   | INDIRECT MEMORY ADDRESSING III-49       |

|     |       | 8.2.7   | I/O PORT ADDRESSING III-49              |

|     | 8.3   | MK38    | 70 INSTRUCTION TYPES III-50             |

|     |       | 8.3.1   | ARITHMETIC AND LOGICAL GROUP III-50     |

|     |       | 8.3.2   | BRANCH, JUMP, CALL, AND RETURN GROUP    |

|     |       | 8.3.3   | ACCUMULATOR DATA MOVEMENT GROUP III-53  |

|     |       | 8.3.4   | ADDRESS REGISTER GROUP                  |

|     |       | 8.3.5   | INPUT/OUTPUT GROUP III-54               |

|     |       | 8.3.6   | CPU CONTROL GROUP III-54                |

|     | 8.4   | INSTR   | UCTION EXECUTION AND TIMING III-60      |

| 9.0 | ) PRC | GRAM    | MING EXAMPLES III-67                    |

|     | 9.1   | INTRO   | DUCTION III-67                          |

|     |       | 9.1.1   | SCRATCHPAD OPERATIONS III-67            |

|     |       | 9.1.2   | DOUBLE PRECISION BINARY ADDITION III-67 |

|     |       | 9.1.3   | DOUBLE PRECISION BINARY NEGATE III-68   |

|     |       | 9.1.4   | SHIFT LEFT DOUBLE                       |

|     |       | 9.1.5   | LOOP COUNTERS                           |

|     |       | 9.1.6   | SINGLE PRECISION MULTIPLICATION ROUTINE |

|     |       | 9.1.7   | MAGNITUDE COMPARISONS                   |

# FIGURE

# PAGE

| 2-1 | 3870 PART NUMBERING EXAMPLE                       |        |

|-----|---------------------------------------------------|--------|

| 3-1 | 3870 FAMILY PIN COMPATIBILITY CHART               |        |

| 4-1 | MK3870 FAMILY BLOCK DIAGRAM                       |        |

| 4-2 | STATUS REGISTER                                   |        |

| 4-3 | 3870 FAMILY PROGRAMMING MODEL                     | III-18 |

| 4-4 | THE ISAR REGISTER                                 |        |

| 4-5 | SCRATCHPAD REGISTER MAP                           | III-20 |

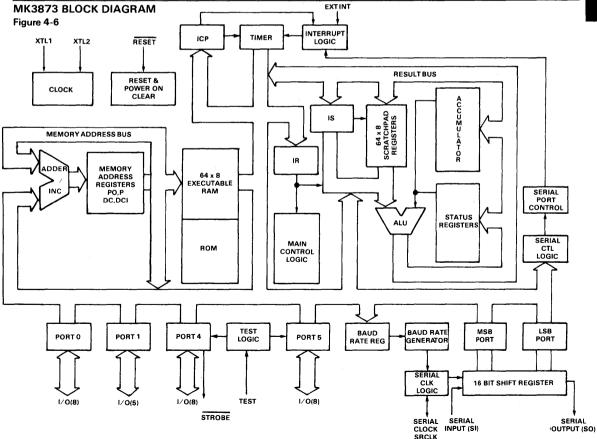

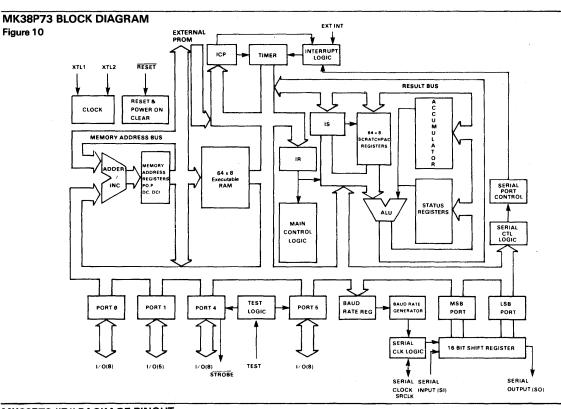

| 4-6 | MK3873 BLOCK DIAGRAM                              |        |

| 4-7 | MK3873 PROGRAMMING MODEL                          |        |

| 4-8 | MK3875 BLOCK DIAGRAM                              |        |

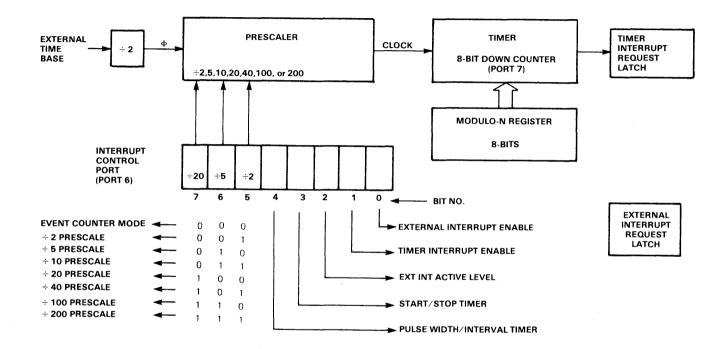

| 5-1 | TIMER AND INTERRUPT CONTROL PORT BLOCK DIAGRAM    |        |

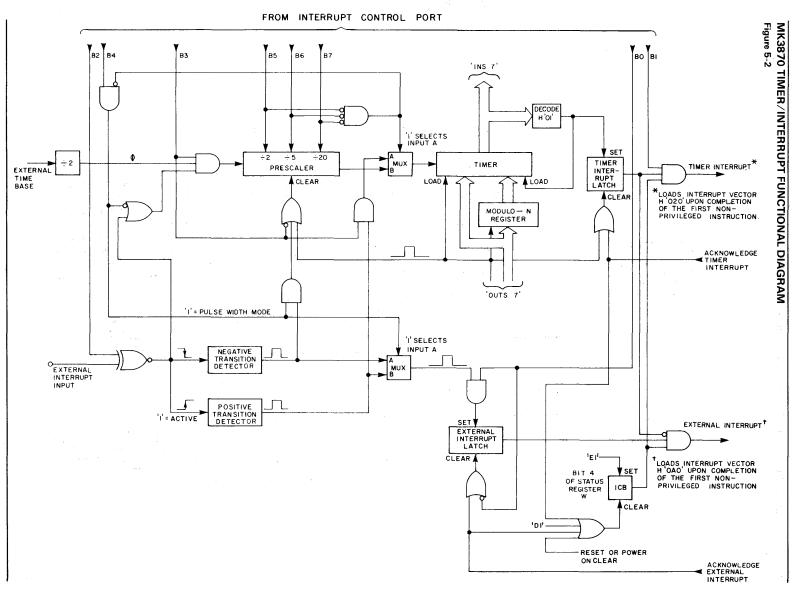

| 5-2 | MK3870 TIMER/INTERRUPT FUNCTIONAL DIAGRAM         |        |

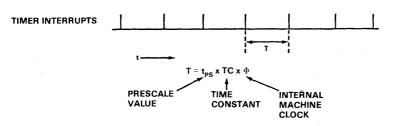

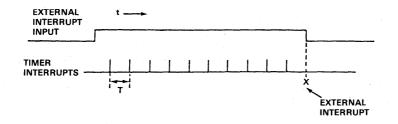

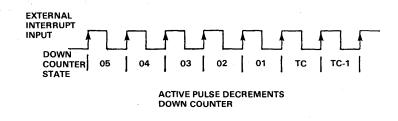

| 5-3 | TIMER OPERATING MODES                             |        |

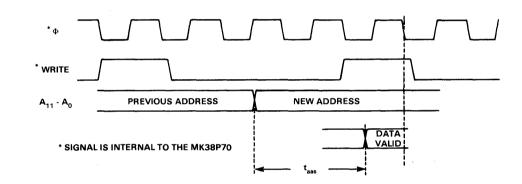

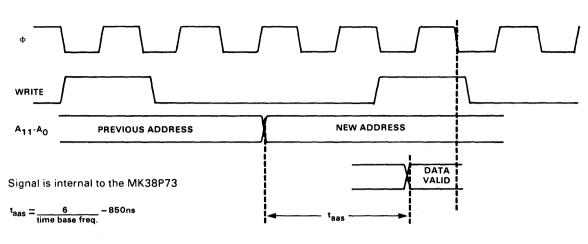

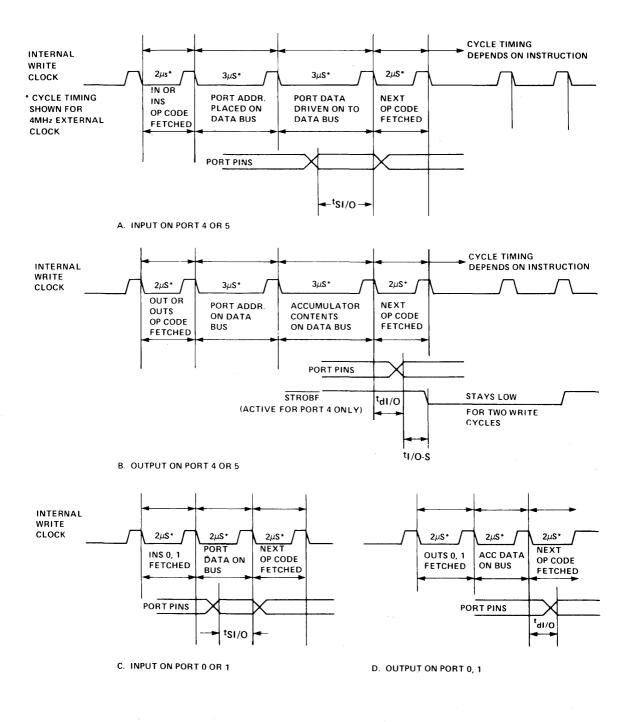

| 6-1 | WRITE CYCLE TIMING                                |        |

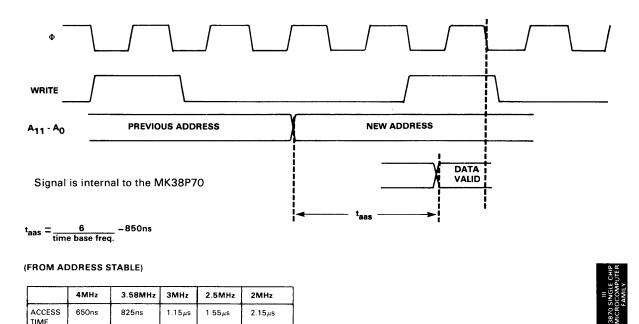

| 6-2 | 38P7X EXTERNAL MEMORY ACCESS CYCLE                | III-34 |

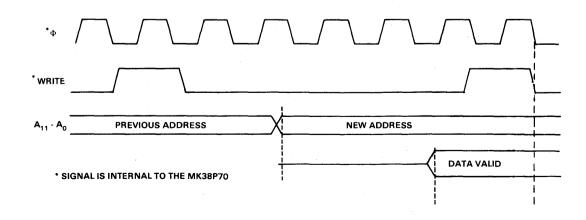

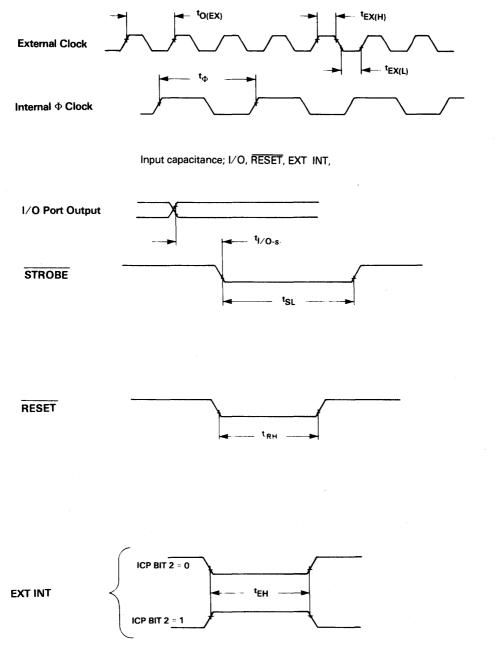

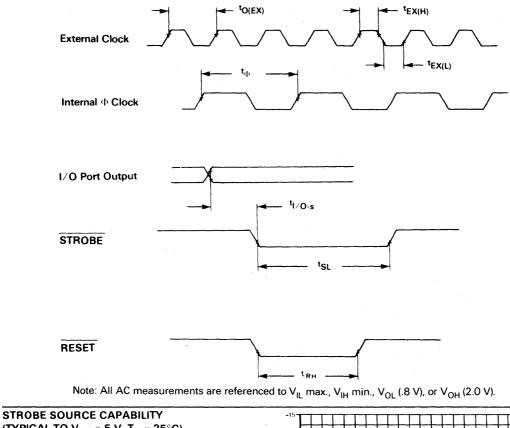

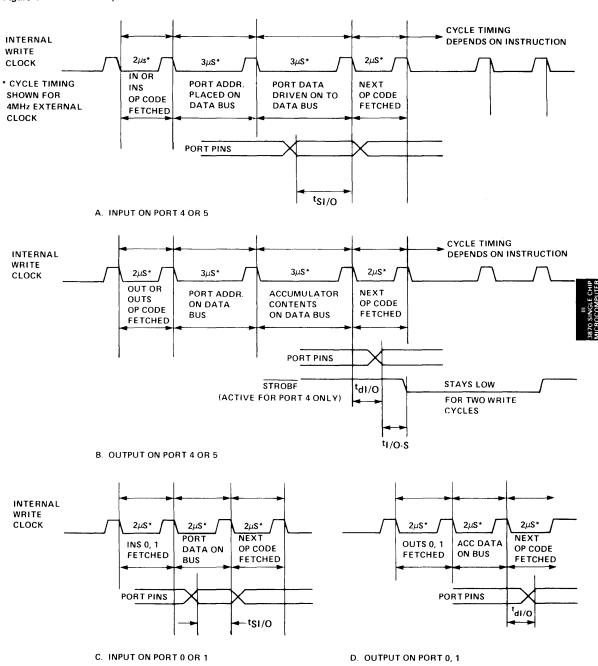

| 6-3 | INPUT/OUTPUT AC TIMING                            | III-36 |

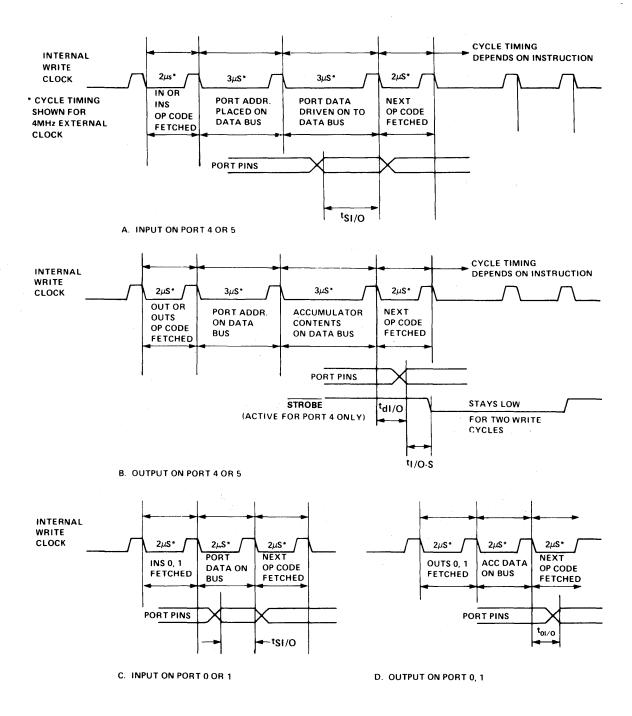

| 6-4 | INTERRUPT SEQUENCE                                | III-38 |

| 6-5 | EXTERNAL INTERRUPT TIMING                         |        |

| 6-6 | RESET HOLD TIME                                   |        |

| 7-1 | MK3870 POWER ON CLEAR BLOCK DIAGRAM               | 111-42 |

| 7-2 | RECOMMENDED RC NETWORK FOR RESET                  | 111-42 |

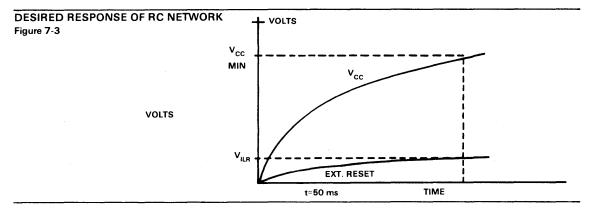

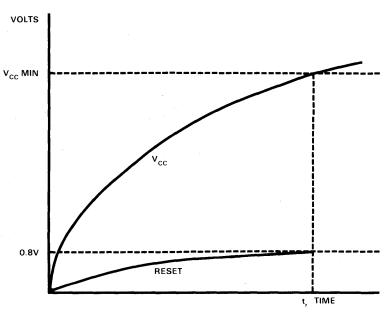

| 7-3 | DESIRED RESPONSE OF RC NETWORK                    | III-43 |

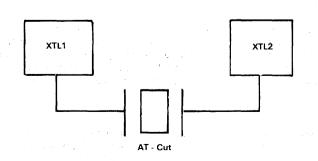

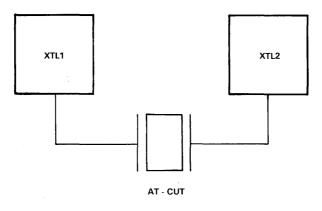

| 7-4 | CRYSTAL MODE CONNECTION                           | 111-44 |

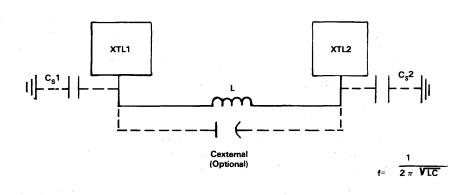

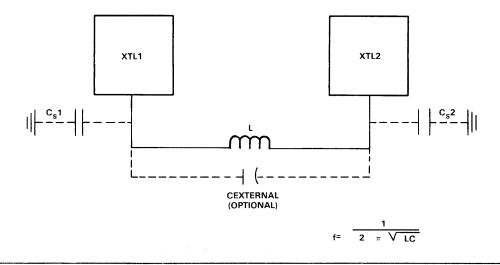

| 7-5 | LC MODE CONNECTION                                | 111-45 |

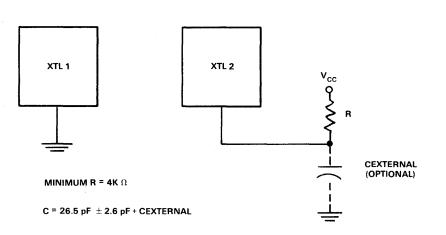

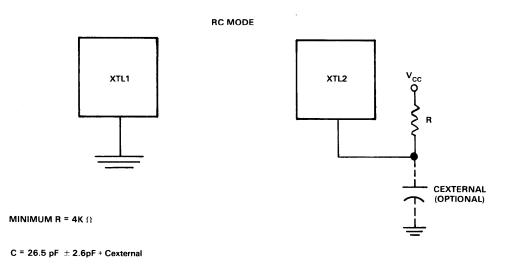

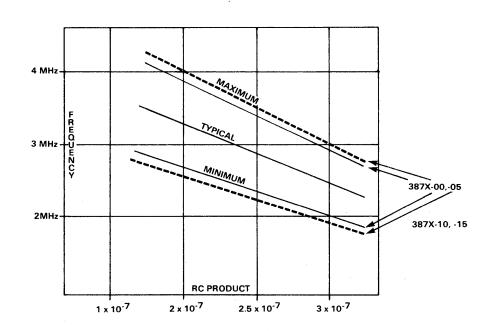

| 7-6 | RC MODE CONNECTION                                | III-46 |

| 7-7 | EXTERNAL MODE CONNECTION                          |        |

| 8-1 | OCTAL REPRESENTATION OF SCRATCHPAD REGISTER ARRAY |        |

| 8-2 | 3870 ADDRESS REGISTER LINKAGES                    | 111-54 |

| 9-1 | CLEAR REGISTER ROUTINE                            |        |

| 9-2 | DOUBLE PRECISION BINARY ADD ROUTINE               |        |

| 9-3 | DOUBLE PRECISION NEGATE ROUTINE                   | III-68 |

| 9-4 | SHIFT LEFT DOUBLE ROUTINE                         | III-69 |

| 9-5 | LOOP COUNTER ROUTINES                             |        |

| 9-6 | MULTIPLICATION ALGORITHM EXAMPLE                  | III-71 |

| 9-7 | MULTIPLICATION ROUTINE                            |        |

| 9-8 | UNSIGNED MAGNITUDE COMPARISON EXAMPLES            |        |

| 9-9 | SIGNED MAGNITUDE COMPARISON EXAMPLES              | 111-74 |

# LIST OF TABLES

# TABLE

# PAGE

| 2-1 | 3870 FAMILY PART NUMBER CROSS REFERENCE     |        |

|-----|---------------------------------------------|--------|

| 2-2 | 3870 SINGLE CHIP MICROCOMPUTER FAMILY       | III-11 |

| 3-1 | PIN FUNCTION SUMMARY                        |        |

| 4-1 | A SUMMARY OF STATUS BITS                    | III-17 |

| 6-1 | MEMORY ACCESS TIME FROM ADDRESS STABLE      | IÌI-35 |

| 8-1 | BRANCH CONDITIONS FOR BT INSTRUCTION        | III-51 |

| 8-2 | BRANCH CONDITIONS FOR BF INSTRUCTION        | III-52 |

| 8-3 | MK3870 INSTRUCTION SET SUMMARY              |        |

| 8-4 | INSTRUCTION TIMING AND EXECUTION            | III-60 |

| 9-1 | STATUS BIT RELATIONS FOR VARIOUS CONDITIONS |        |

### **1.0 INTRODUCTION**

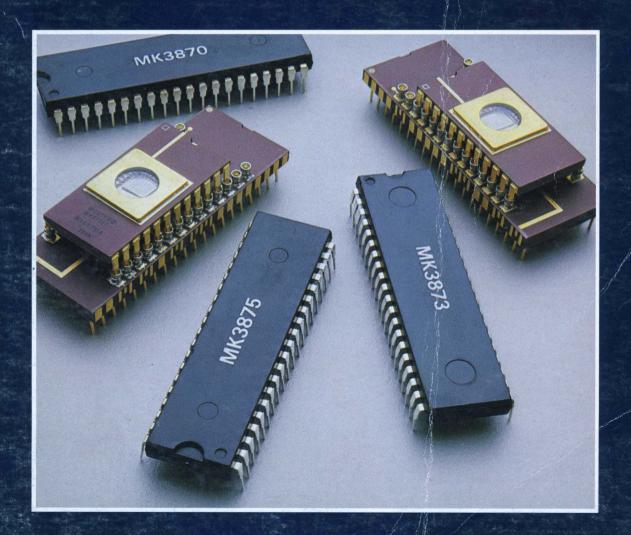

The MK3870 Family of Single Chip Microcomputers are complete, 8 bit microcomputers implemented on a single MOS integrated circuit. These microcomputers are ideal for use as logic replacement elements in a variety of control applications. Features which are common among devices in the MK3870 Family are listed listed below:

- Common instruction set consisting of over 70 instruction types.

- □ Versions with various combinations of ROM and executable RAM.

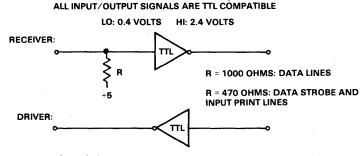

- $\Box$  Up to 32 bits (4 ports) TTL compatible I/O.

- Programmable binary timer

Interval Timer Mode

Pulse Width Measurement Mode

Event Counter Mode

- External interrupt input.

- Crystal, LC, RC, or External time base options available

- □ EPROM compatible versions available for development, prototyping, and low-volume production.

- Pinout compatibility (In Socket Expandibility)

- Low power dissipation.

- □ Single +5 volt power supply.

Members in the MK3870 Family require only a single +5V power supply and dissipate very little power. Utilizing ion-implanted, N-channel silicon gate technology and advanced circuit design techiques, MK3870 Family devices offer maximum cost effectiveness in a wide range of applications.

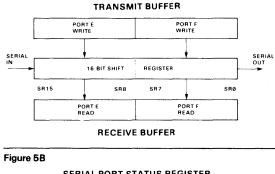

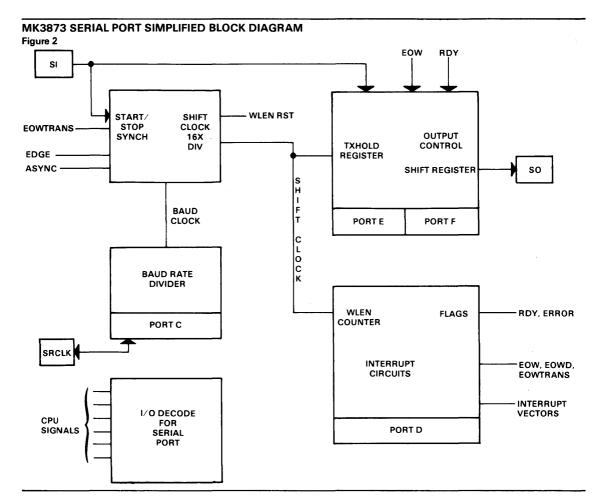

All MK3870 Family microcomputers execute a common set of more than 70 instructions. These devices are available in a wide range of memory sizes and types so that a designer can choose a device with the right combination of ROM and RAM to suit his system requirements. In addition, MK3870 Family devices are available with special types of I/O, such as the 3873 with an on chip, sixteen bit serial I/O port. All devices in the family are pin compatible, a feature which allows easy system upgrade by replacing a MK3870 device in an existing design with another in the family with greater amounts of ROM and/or RAM or special I/O functions.

This ease of system upgrade is a concept known as In Socket Expandibility. In Socket Expandibility provides the designer with a new concept in system expansion. With In Socket Expandability, microcomputer based systems can be enhanced or expanded in many different ways without affecting the printed circuit board, the enclosure, or power supply requirements for the system. The Mostek MK3870 Microcomputer Family implements the concept of In Socket Expandibility to provide low design costs. Manufacturers who have used the MK3870 in product designs can extend the products capability simply by removing the MK3870 microcomputer from its socket and replacing it with another member of the MK3870 Microcomputer Family.

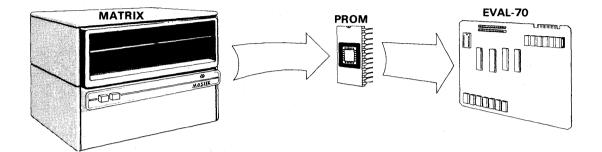

Mostek supplies a complete line of development equipment and associated software support packages which can be used as tools for writing and debugging MK3870 programs. For the user who requires a sophisticated development system, the MATRIX (TM) dual floppy disk based development system is available which is based on the powerful Mostek Z80 chip set. A macro cross-assembler for the MK3870 instruction set, called MACRO-70, is available which runs under FLP-80DOS, the operating system for the MATRIX. MACRO-70 is the most powerful macro assembler on the microcomputer market, and features a number of macro definitions on diskette which can be used to extend the base instruction set of the 3870. Use of MACRO-70 can result in guicker generation of MK3870 programs. The AIM-73E Application

Interface Module is a systems product which is directly interfaced with the MATRIX and provides real time in-circuit-emulation for all devices in the MK3870 Family. The AIM-73E standard features include breakpoint, single step, and display and modification of the contents of any memory location, register, or I/O port. In addition, the AIM-73E has a 1048 x 48 history trace memory which can be used to capture up to 1048 cycles of program execution.

The Mostek MK3870 Family of single chip microcomputers is recognized as an industry standard in logic replacement. The MK3870 has been designed into and successively used in a wide range of applications which require some type of intelligent control. The MK3870 has made possible a whole new technology that can create cost effective system solutions to manufacturers of automobiles, major appliances, industrial controls, computer peripherals, and more. New and more powerful products have been added to the MK3870 Family, making even more applications practical and affordable.

### 2.0 PART IDENTIFICATION

## 2.1 USING THE TECHNICAL MANUAL

The MK3870 Family Technical Manual is provided as an overall user's guide to the operation and application of MK3870 Family products. It is intended to provide detailed technical information on those features which are common to all (or several) devices in the family. Additional information is provided which covers briefly features that apply to a specific group of devices in the 3870 Family. For example, an overview of the MK3873's serial I/O port logic is given in the technical manual, but the MK3873 data sheet should be consulted for detailed operation and programming of the serial I/O port. In some sections of the technical manual, certain electrical and timing specifications are referred to in the discussion of a subject such as the selection of a crystal. Again, the user should still consult the appropriate device data sheet for exact specifications.

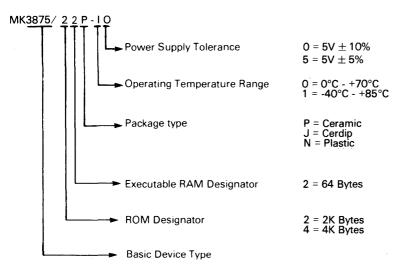

## 2.2 PART NUMBERING SYSTEM

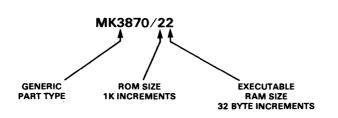

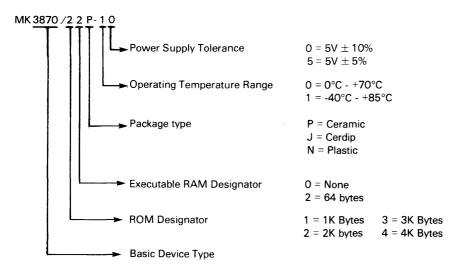

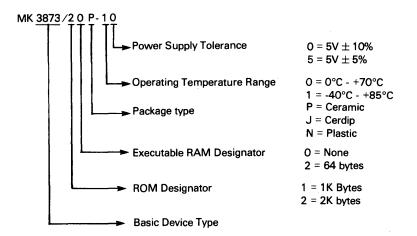

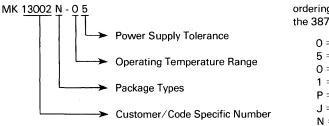

Since a number of new devices are continually being added to the 3870 Family, a new part numbering system has been implemented by Mostek. This part numbering system uses a generic number to designate a particular pin configuration and technology of a 3870 Family device, followed by a slash number which represents the amount and type of memory implemented on that device. An example of this part numbering system is illustrated in Figure 2-1.

### 3870 PART NUMBERING EXAMPLE Figure 2-1

The two digit slash number specifies the size of ROM and RAM on the chip. The left digit represents the amount of ROM on chip in increments of 1K bytes. The right digit represents the amount of executable RAM on chip in increments of 32 bytes. Note that all 3870 devices have 64 bytes of scratchpad RAM which is not included in the slash number designation, since it is not addressed as main memory. Only the RAM memory which is addressed in the same memory space as ROM is indicated by the slash number.

At present, there are three generic types of 3870 Family devices which are available in various combinations of ROM and RAM as specified in the two-digit slash number suffix. These three types of devices are listed below:

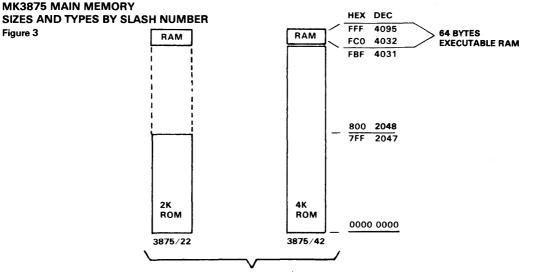

MK3870/XX - 32 bits of bidirectional, parallel I/O MK3873/XX - Serial I/O port microcomputer MK3875/XX - Battery backup microcomputer

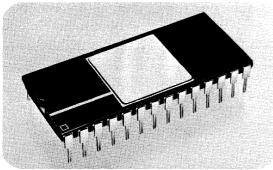

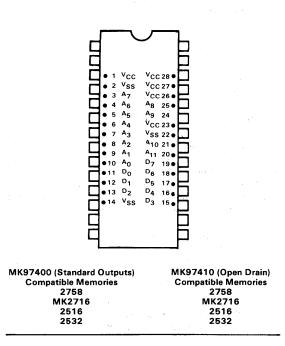

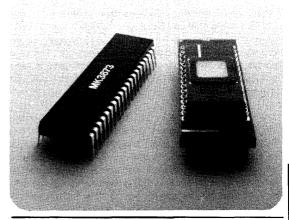

Mostek also offers a full line of EPROM compatible 3870's. A special packaging technology has been developed which allows a standard 24 pin or 28 pin EPROM memory to be plugged directly into the back of the 40 pin package. This special type of package has been termed the Piggyback PROM or P-PROM (TM) package. The Mostek part numbering system specifies a P-PROM device with the designation 38P7X where the "X" represents the generic part type being emulated. For example, the P-PROM device which can be used to emulate a 3870 mask ROM microcomputer would be a 38P70. All P-PROM devices have an identical pinout as the mask ROM device they emulate.

A product which has recently been announced by MOSTEK is a CMOS version of the 3870 which will be designated as the MK38C70. The first CMOS device which is intended to be made available is the P-PROM equivalent which is called the MK38CP70. The 38CP70 will allow exact emulation of the mask ROM device.

Since many users are probably familiar with the old part numbering system of 3870 Family single chip microcomputers, the following cross reference guide shown in Table 2-1 is provided as an aid in determining the new part number from the old designation. Also, the list shown in Table 2-2 is provided as a summary of devices which are now available or soon to be available in the MK3870 single chip microcomputer family.

### 3870 FAMILY PART NUMBER CROSS REFERENCE Table 2-1

| Old Part<br>Number            | New Part<br>Number | ROM  | Executable<br>RAM | Parallel<br>I/ O | Special<br>I/ O | Technology         |

|-------------------------------|--------------------|------|-------------------|------------------|-----------------|--------------------|

| MK3870                        | MK3870/20          | 2K   | 0 bytes           | 32 bits          |                 | NMOS               |

| MK3872                        | MK3870/42          | 4К   | 64 bytes          | 32 bits          | -               | NMOS               |

| MK3872<br>w∕standby           | MK3875/42          | 4K   | 64 bytes          | 30 bits          | $V_{SB'}V_{BB}$ | NMOS               |

| MK3873                        | MK3873/20          | 2К   | 0 bytes           | 29 bits          | SI,SO,<br>SRCLK | NMOS               |

| MK3874<br>MK97400,<br>MK97401 | MK38P70/02         | Ext. | 64 bytes          | 32 bits          | -               | NMOS<br>P-PROM pkg |

| MK3876                        | MK3870/22          | 2К   | 64 bytes          | 32 bits          | -               | NMOS               |

| MK3876<br>w/standby           | MK3875/22          | 2К   | 64 bytes          | 30 bits          | $V_{SB'}V_{BB}$ | NMOS               |

|                               |                    |      |                   |                  |                 |                    |

# 3870 SINGLE CHIP MICROCOMPUTER FAMILY Table 2-2

| Device      | ROM<br>(bytes) | Scratchpad<br>RAM | Executable<br>RAM | Parallel<br>I/ O | Special<br>I/O                   | Technology          |

|-------------|----------------|-------------------|-------------------|------------------|----------------------------------|---------------------|

| MK3870/10   | 1K             | 64 bytes          | 0 bytes           | 32 bits          | -                                | NMOS                |

| MK3870/12   | 1K             | 64 bytes          | 64 bytes          | 32 bits          | -                                | NMOS                |

| MK3870/20   | 2K             | 64 bytes          | 0 bytes           | 32 bits          | -                                | NMOS                |

| MK3870/22   | 2K             | 64 bytes          | 64 bytes          | 32 bits          | -                                | NMOS                |

| MK3870/30   | ЗК             | 64 bytes          | 0 bytes           | 32 bits          | -                                | NMOS                |

| MK3870/32   | ЗК             | 64 bytes          | 64 bytes          | 32 bits          | -                                | NMOS                |

| MK3870/40   | 4K             | 64 bytes          | 0 bytes           | 32 bits          | -                                | NMOS                |

| MK3870/42   | 4K             | 64 bytes          | 64 bytes          | 32 bits          | -                                | NMOS                |

| MK3873/10   | 1K             | 64 bytes          | 0 bytes           | 29 bits          | SI,SO<br>SRCLK                   | NMOS                |

| MK3873/12   | 1K             | 64 bytes          | 64 bytes          | 29 bits          | SI,SO<br>SRCLK                   | NMOS                |

| MK3873/20   | 2К             | 64 bytes          | 0 bytes           | 29 bits          | SI,SO<br>SRCLK                   | NMOS                |

| MK3873/22   | 2K             | 64 bytes          | 64 bytes          | 29 bits          | SI,SO<br>SRCLK                   | NMOS                |

| MK3875/22   | 2K             | 64 bytes          | 64 bytes          | 30 bits          | V <sub>SB</sub> ,V <sub>BB</sub> | NMOS                |

| MK3875/42   | 4K             | 64 bytes          | 64 bytes          | 30 bits          | V <sub>SB</sub> ,V <sub>BB</sub> | NMOS                |

| MK38C70/10  | 1K             | 64 bytes          | 0 bytes           | 32 bits          | -                                | CMOS                |

| MK38C70/20  | 2K             | 64 bytes          | 0 bytes           | 32 bits          | -                                | CMOS                |

| MK38P70/02  | Ext.           | 64 bytes          | 64 bytes          | 32 bits          | -                                | NMOS<br>P-PROM pkg. |

| MK38P73/02  | Ext.           | 64 bytes          | 64 bytes          | 29 bits          | SI,SO<br>SRCLK                   | P-PROM pkg.         |

| MK38CP70/02 | Ext.           | 64 bytes          | 64 bytes          | 32 bits          | -                                | CMOS<br>P-PROM pkg. |

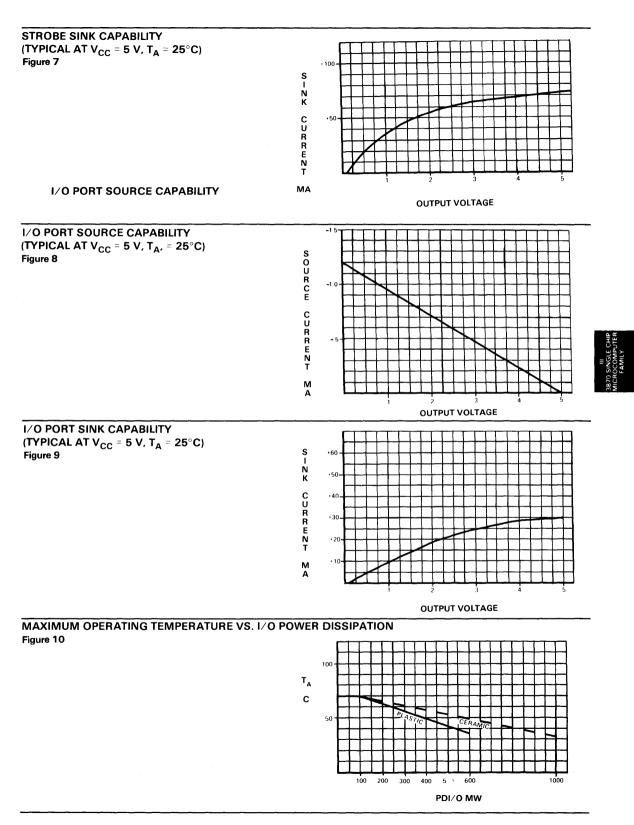

# III 3870 SINGLE CH MICROCOMPUTI

# 3.0 FUNCTIONAL PIN DESCRIPTION

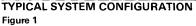

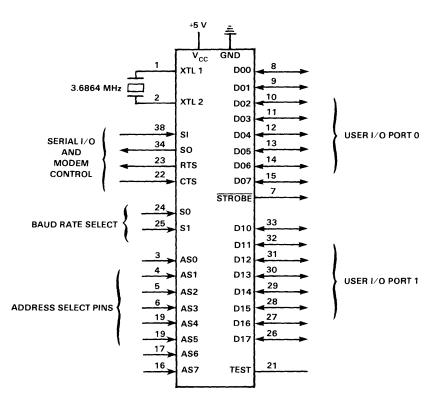

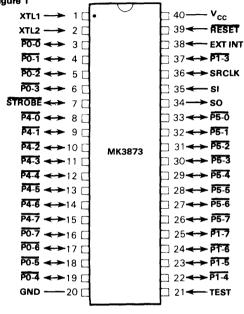

The chart shown in Figure 3-1 pictures the pin configuration for the three generic part types currently available in the 3870 Family. MK3870 Family microcomputers exhibit the feature of universal pin compatibility. All devices in the Family are complete, 8-bit microcomputer systems implemented on a single integrated circuit chip so that the majority of pins are dedicated to I/O. Some devices differ slightly in terms of pin functions in cases where special I/O functions have been implemented.

The pin designation shown in the chart for devices with the generic part number "3870" represent those which have a full 32 bits of bidirectional, parallel I/O which are addressed as four 8 bit ports. The "3873" number represents those devices which have 3 lines dedicated to a serial I/O function along with 29 bits of parallel I/O. "3875" devices have two pins which serve as the standby power option lines for saving the contents of executable RAM in a low power standby mode.

# 3870 FAMILY PIN COMPATIBILITY CHART Figure 3-1

| 3873 | 3875   | 38C70 | 3870 |      |       |     | 3870 | 38C70    | 3875     | 3873     |

|------|--------|-------|------|------|-------|-----|------|----------|----------|----------|

| 3073 | - 3875 | 38070 |      |      | ····· | 140 |      | 30070    | 3075     | 5075     |

|      |        |       | X1   |      |       | 40  | VCC  |          |          |          |

|      |        |       | X2   | 2    |       | 39  | RST  | I        | 1        |          |

|      | VBB    |       | P0-0 | 3    |       | 38  | INT  |          |          |          |

|      | VSB    |       | P0-1 | 4    |       | 37  | P1-0 |          |          |          |

|      |        |       | P0-2 | 5    |       | 36  | P1-1 |          | 1        | SRCLK    |

|      | 1      |       | P0-3 | 6    |       | 35  | P1-2 | 1        |          | SI       |

|      |        |       | STB  | 7    |       | 34  | P1-3 | 1        | 1        | SO       |

|      | -      |       | P4-0 | 8    |       | 33  | P5-0 |          |          |          |

|      |        |       | P4-1 | 9    |       | 32  | P5-1 |          |          | 1        |

|      |        |       | P4-2 | 10   |       | 31  | P5-2 | 1        | 1        | 1        |

|      |        |       | P4-3 | 1 11 |       | 30  | P5-3 | 1        | 1        |          |

|      | -      |       | P4-4 | 12   |       | 29  | P5-4 | 1        | 1        |          |

|      | 1      | 1     | P4-5 | 13   |       | 28  | P5-5 | 1        | 1        |          |

|      |        |       | P4-6 | 14   |       | 27  | P5-6 | <u> </u> |          |          |

|      |        |       | P4-7 | 15   |       | 26  | P5-7 |          | 1        |          |

|      | -      | 1.    | P0-7 | 16   |       | 25  | P1-7 |          | 1        | 1        |

|      | -1     |       | P0-6 | 17   |       | 24  | P1-6 | l        | 1        | 1        |

|      |        |       | P0-5 | 18   |       | 23  | P1-5 | I        | <u> </u> | 1        |

|      | 1      | +     | P0-4 | 19   |       | 22  | P1-4 | <u> </u> | ł        | 1        |

|      |        |       | GND  | 20   |       | 21  | TEST |          | ł        | <u> </u> |

|      |        |       | UND  | 201  |       | 121 | 1231 | 1        |          | 1        |

The following is a description of the function of each pin associated with the MK3870, the base 3870 Family part type:

#### PIN FUNCTION SUMMARY Table 3-1

| PIN NAME    | DESCRIPTION        | ТҮРЕ          |

|-------------|--------------------|---------------|

| PO-0 - PO-7 | I/O Port 0         | Bidirectional |

| P1-0 - P1-7 | I/O Port 1         | Bidirectional |

| P4-0 - P4-7 | I/O Port 4         | Bidirectional |

| P5-0 - P5-7 | I/O Port 5         | Bidirectional |

| STROBE      | Ready Strobe       | Output        |

| EXT INT     | External Interrupt | Input         |

| RESET       | External Reset     | Input         |

# PIN FUNCTION SUMMARY

| Table 3-1 (Continued) |                      |               |  |

|-----------------------|----------------------|---------------|--|

| PIN NAME              | DESCRIPTION          | TYPE          |  |

| TEST                  | Test Line            | Input         |  |

| XTL 1, XTL2           | Time Base            | Input         |  |

| SI                    | Serial Input         | Input         |  |

| SO                    | Serial Output        | Output        |  |

| SRCLK                 | Serial Clock         | Bidirectional |  |

| V <sub>SB</sub>       | Standby Power        | Input         |  |

| VBB                   | Substrate Decoupling | Input         |  |

| V <sub>CC</sub> , GND | Power Supply Lines   | Input         |  |

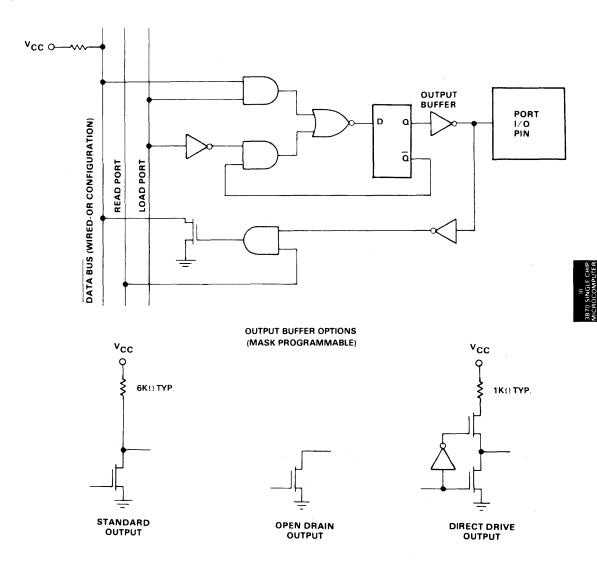

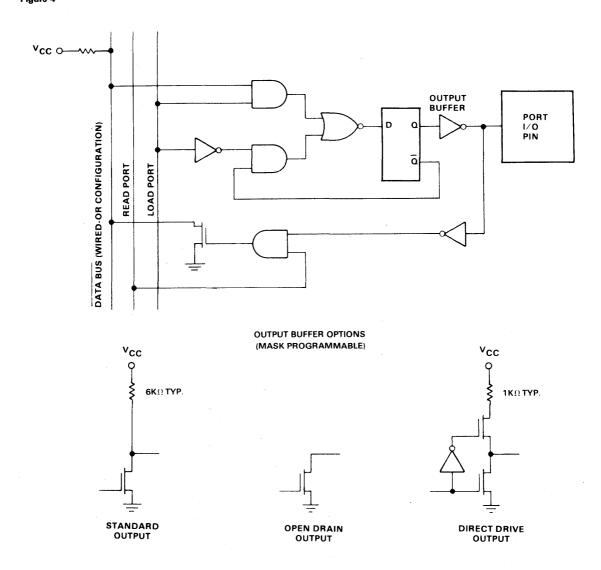

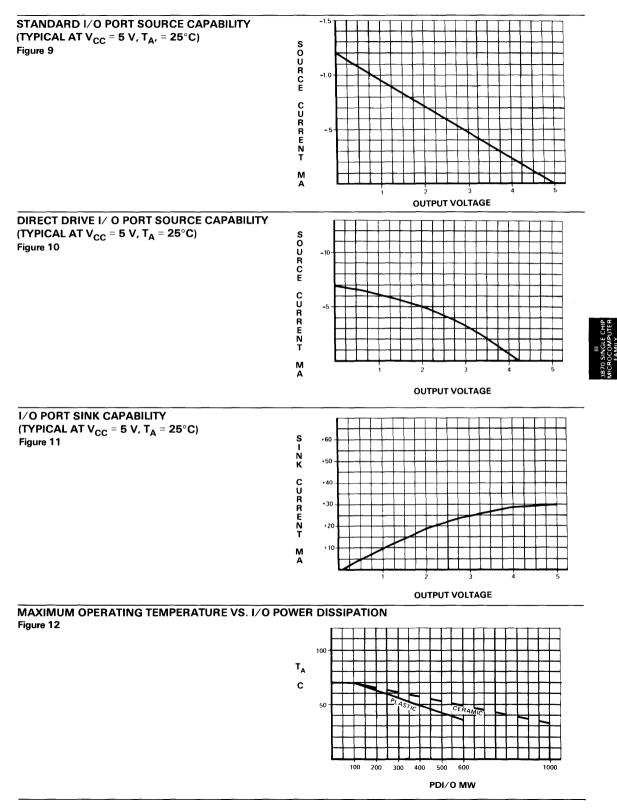

PO-0—PO-7, P1-0—P1-7, P4-0—P4-7, and P5-0—P5-7 are 32 lines which can be individually used as either TTL compatible inputs or as latch outputs.

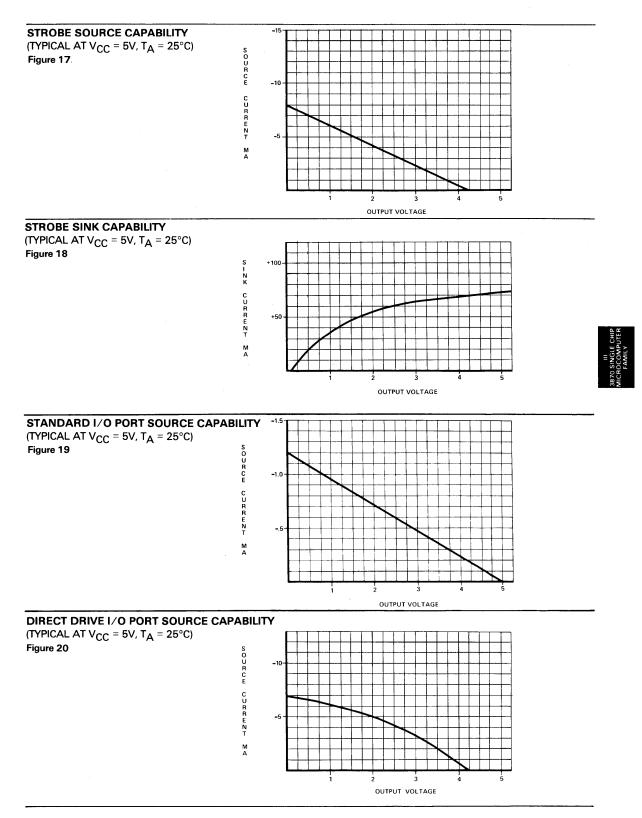

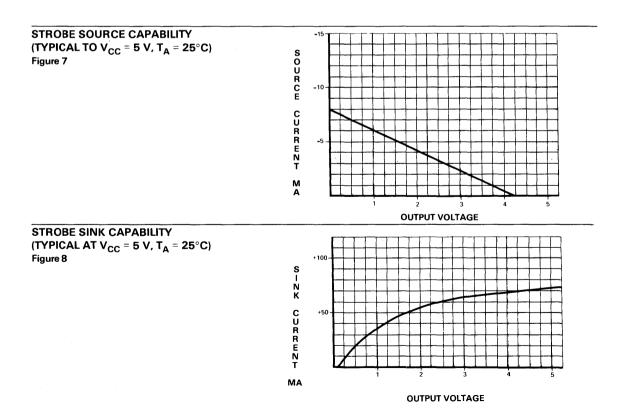

STROBE is a ready strobe associated with I/O Port 4. This pin which is normally high provides a single low pulse after valid data is present on the P4-0—P4-7 pins during an output instruction.

RESET may be used to externally reset the 3870. When pulled low the 3870 will reset. When then allowed to go high the 3870 will begin program execution at program location H '000'.

EXT INT is the external interrupt input. Its active state is software programmable. This input is also used in conjunction with the timer for pulse width measurement and event counting.

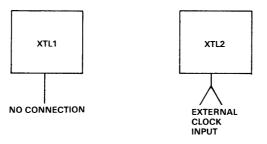

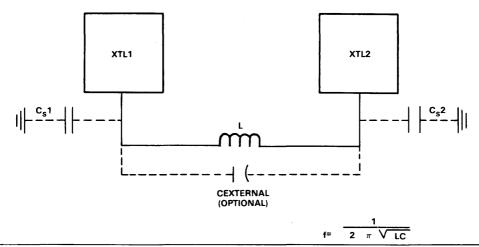

XTL 1 and XTL 2 are the time base inputs to which a crystal, LC network, RC network, or an external single-phase clock may be connected.

TEST is an input, used only in testing the 3870. For normal circuit functionality this pin is left unconnected or may be grounded.

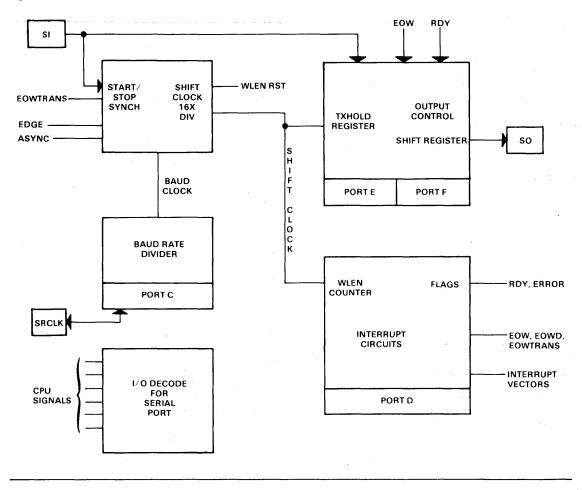

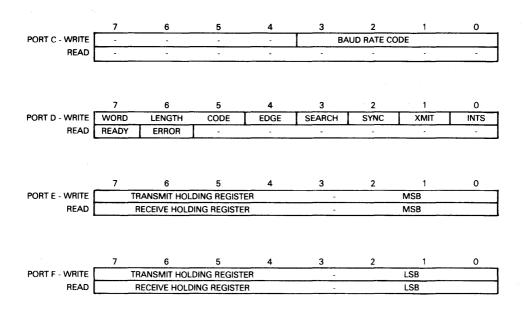

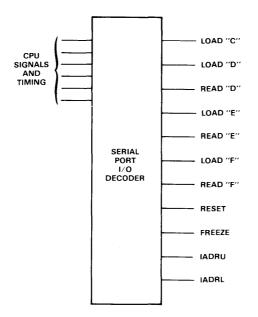

SI is a serial input line and exists only on MK3873/XX devices. It is the data input to the serial port of the MK3873.

SO is a serial output line and exists only on MK3873/XX devices. It is the data output of the serial I/O port of the MK3873.

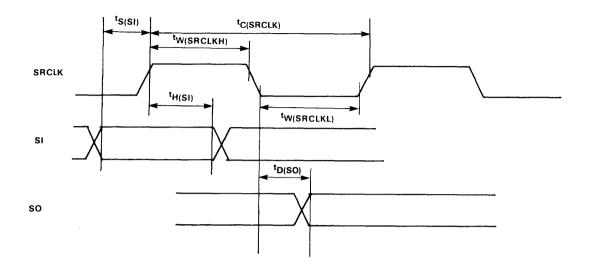

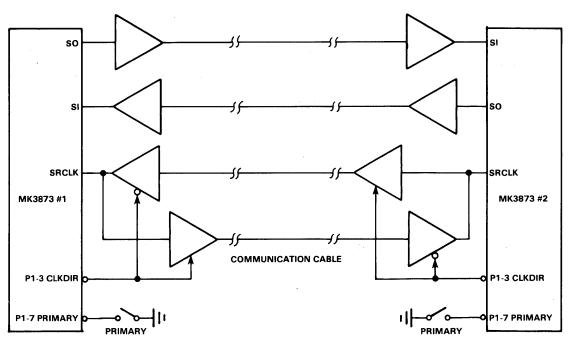

SRCLK is the clock for the serial port and exists only on MK3873/XX devices. It can be programmed by software as an input or an output so that the serial port may be driven from the internal baud rate generator or from an external source.

V<sub>SB</sub> is the auxilliary power supply input used only on MK3875/XX devices.

$V_{BB}$  is the substrate decoupling pin used only on MK3875/XX devices. A capacitor is required to be tied from  $V_{BB}$  to ground.

V<sub>CC</sub> is the power supply input.

### 4.0 MK3870 ARCHITECTURE

### 4.1 INTRODUCTION

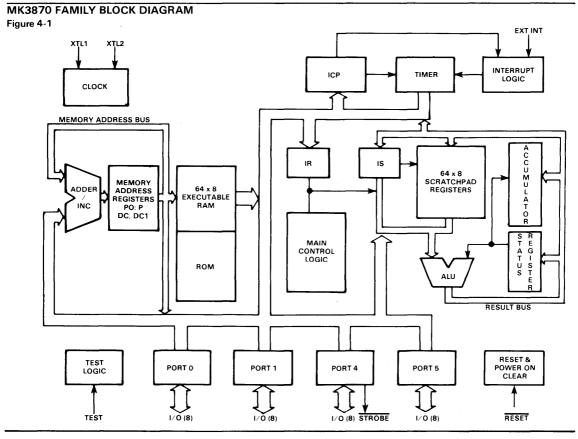

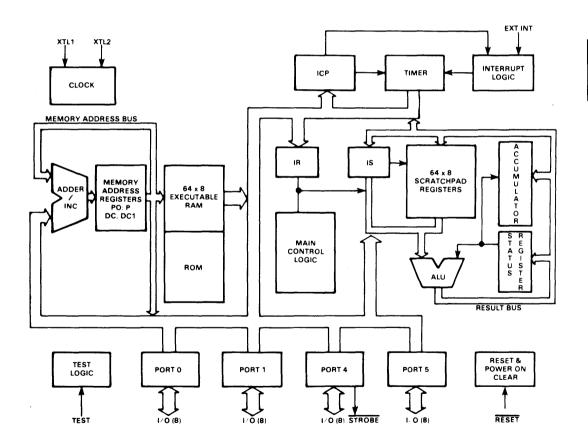

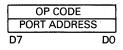

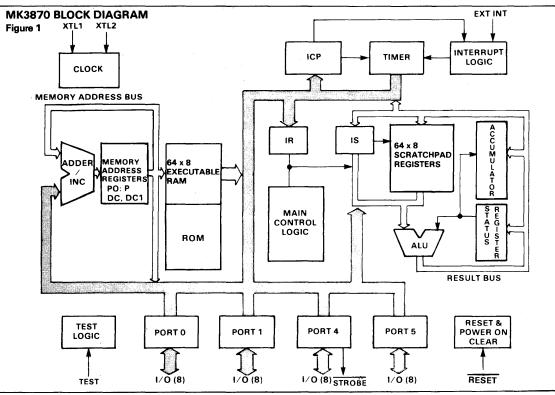

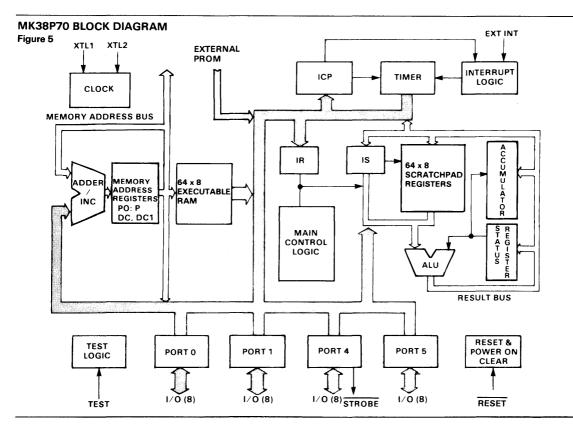

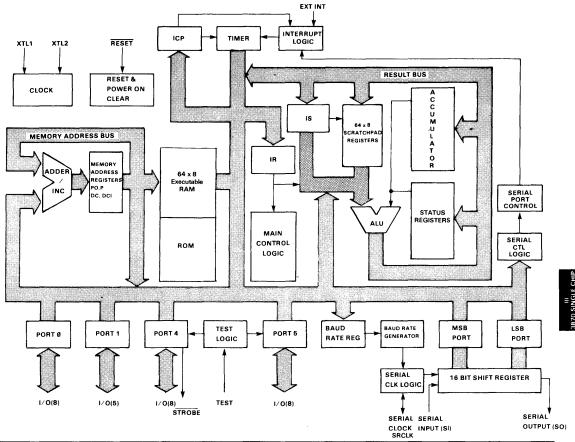

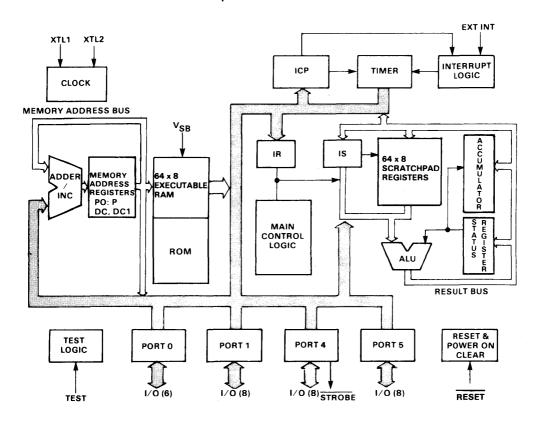

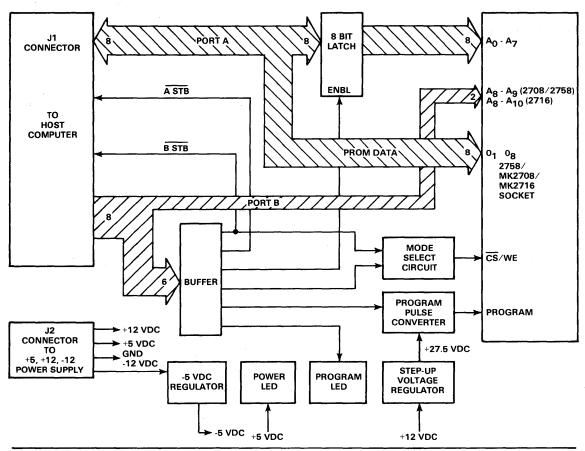

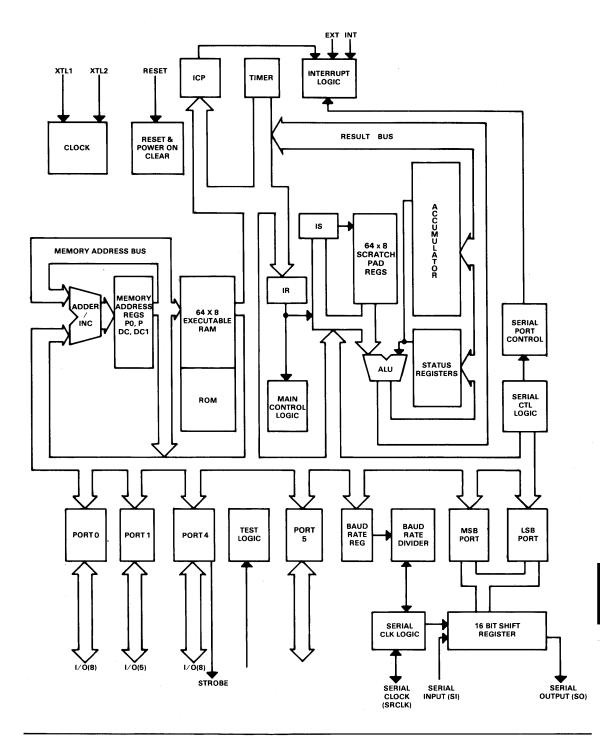

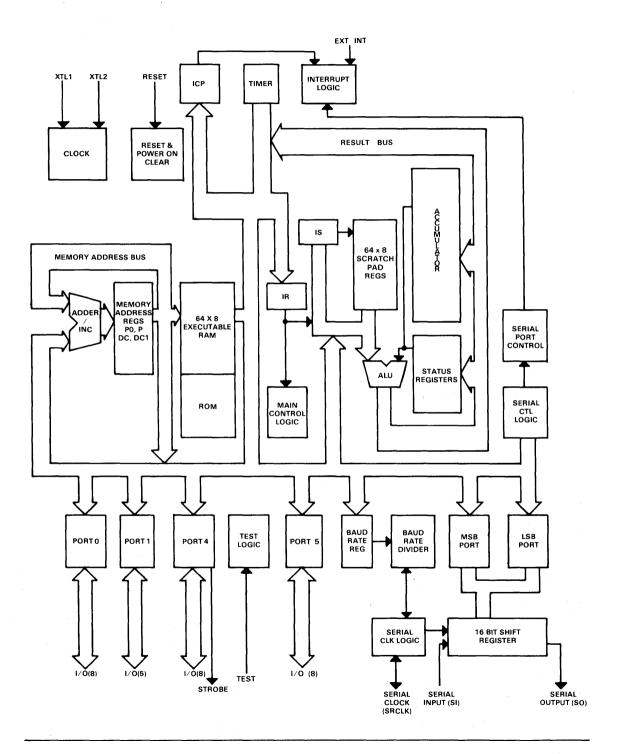

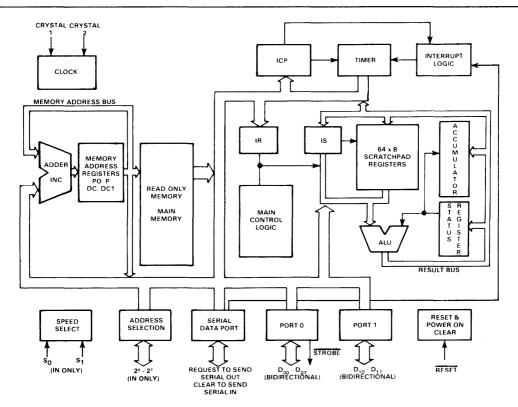

All members of the MK3870 Single Chip Microcomputer Family share a common architecture. This section describes the basic functional elements of the 3870 Family architecture. Elements of the architecture which are common to all 3870 Family devices are discussed in sections 4.2-4.9. A block diagram which depicts the MK3870 is shown in Figure 4-1, along with a programming model which is pictured in Figure 4-3. Section 4.10 contains a brief description of the MK3873 serial I/O port, and Section 4.11 briefly describes the battery backup feature of the MK3875.

# 4.2 MAIN CONTROL LOGIC

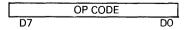

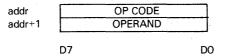

The Instruction Register (IR) receives the operation code (OP code) of the instruction to be executed from the program ROM via the data bus. The OP code is loaded into the instruction register from the internal data bus at the end of the execution sequence for the previous instruction.

OP codes in the 3870 are either 4 or 8 bits long. In those instructions in which the OP code is 4 bits long, the lower 4 bits are either used as an immediate address to an I/O port or scratchpad location or as an immediate 4 bit operand. Once latched into the IR the main control logic decodes the instruction and provides the necessary gating signals to all circuit elements.

# 4.3 ARITHMETIC AND LOGIC UNIT (ALU)

After receiving commands from the main control logic, the ALU performs the required arithmetic or logic operations (using the data presented on the two input busses) and provides the result on the result bus. The arithmetic operations that can be performed in the ALU are binary add, decimal

adjust, add with carry, decrement, and increment. The logic operations that can be performed are AND, OR, EXCLUSIVE OR, 1's complement, shift right, and shift left. Besides providing the result on the result bus, the ALU also provides four signals representing the status of the result. These signals, stored in the Status Register (W), represent CARRY, OVERFLOW, SIGN, and ZERO condition of the result of the operation.

#### 4.4 ACCUMULATOR (A)

The Accumulator (A) is the principal register for data manipulation within the 3870. The A serves as one input to the ALU for arithmetic or logical operations. The result of ALU operations are stored in the Accumulator.

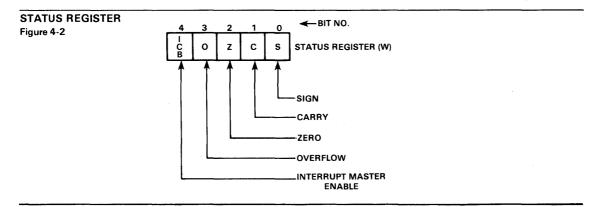

## 4.5 THE STATUS REGISTER (W)

The Status Register (also called the W register) holds five status flags as shown below in Figure 4-2.

#### 4.5.1 SIGN (S BIT)

When the results of an ALU operation are being interpreted as a signed binary number, (2's complement representation) the high order bit (bit 7) represents the sign of the number. At the conclusion of instructions that may modify the Accumulator most significant bit, (bit 7) the S bit is set to the complement of the result of the operation.

#### 4.5.2 CARRY (C BIT)

The C bit may be visualized as an extension of an 8-bit data unit, i.e., the ninth bit of a 9-bit data unit. When two bytes are added, and the sum is greater than 255, then the carry out of the high order bit appears in the C bit. Here are some examples:

|                        | С   | 7       | 6      | 5      | 4      | 3     | 2     | 1 | 0 | <- Bit Number |

|------------------------|-----|---------|--------|--------|--------|-------|-------|---|---|---------------|

| Accumulator contents : |     | 0       | 1      | 1      | 0      | 0     | 1     | 0 | 1 |               |

| Value added :          |     | 0       | 1      | 1      | 1      | 0     | 1     | 1 | 0 |               |

| Sum :                  | 0   | 1       | 1      | 0      | 1      | 1     | 0     | 1 | 1 |               |

|                        |     |         |        |        |        |       |       |   |   |               |

|                        | The | re is i | no car | ry, so | C is r | reset | to 0. |   |   |               |

|                        |     |         |        |        |        |       |       |   |   |               |

|                        | С   | 7       | 6      | 5      | 4      | 3     | 2     | 1 | 0 | <- Bit Number |

| Accumulator contents : |     | 1       | 0      | 0      | 1      | 1     | 1     | 0 | 1 | *             |

| Value added :          |     | 1       | 1      | 0      | 1      | 0     | 0     | 0 | 1 |               |

| Sum :                  | 1   | 0       | 1      | 1      | 0      | 1     | 1     | 1 | Õ |               |

|                        |     |         |        |        |        |       |       |   |   |               |

There is a carry, so C is set to 1.

#### 4.5.3 ZERO (Z BIT)

The Z bit is set whenever an arithmetic or logical operation generates a zero result. The Z bit is reset to 0 when an arithmetic of logical operation could have generated a zero result, but did not.

# 4.5.4 OVERFLOW (O BIT)

When the results of an ALU operation are being interpreted as a signed binary number (2's complement representation), some method must be provided for indicating carries out of the highest numeric bit (bit 6). This is done using the O bit. After arithmetic operations, the O bit is set to the Exclusive-OR of carries out of bits 6 and 7. The fact that this simplifies signed binary arithmetic is described in the MK3870 Family Programming Manual. Here are some examples:

|                        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | <- Bit Number |

|------------------------|---|---|---|---|---|---|---|---|---------------|

| Accumulator contents : | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |               |

| Value added :          | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |               |

| Sum :                  | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |               |

| 1                      |   |   |   |   |   |   |   |   |               |

There is a carry out of bit 6 and out of bit 7, so the O bit is reset to 0(1 + 1 = 0). The C bit is set to 1.

|                        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | <- Bit Number |

|------------------------|---|---|---|---|---|---|---|---|---------------|

| Accumulator contents : | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |               |

| Value added :          | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |               |

| Sum :                  | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |               |

There is a carry out of bit 6, but no carry out of bit 7; the O bit is set to 1 (1 + 0 = 1). The C bit is reset to 0.

#### 4.5.5 INTERRUPTS (ICB BIT)

External logic can alter program execution sequence within the CPU by interrupting ongoing operations, as described in Section 5; however, interrupts are allowed only when the ICB bit is set to 1; interrupts are disallowed when the ICB bit is reset to 0.

#### A SUMMARY OF STATUS BITS Table 4-1

| OVERFLOW | = CARRY + CARRY                                       |

|----------|-------------------------------------------------------|

| ZERO     | = ALU & ALU |

| CARRY    | = CARRY <sub>7</sub>                                  |

| SIGN     | = ALU                                                 |

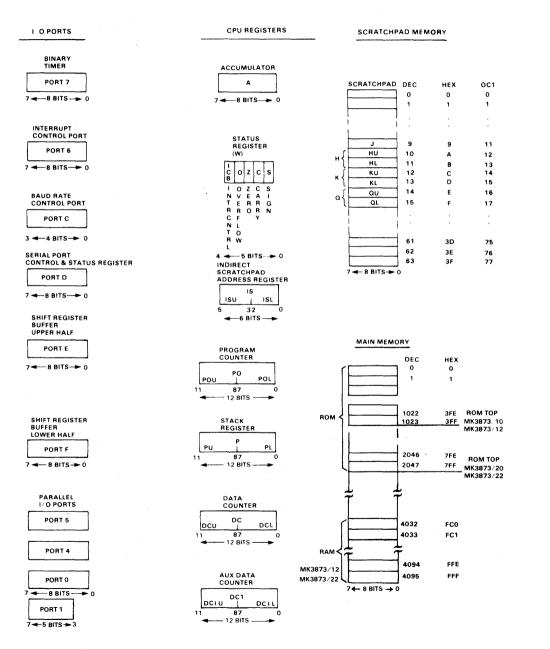

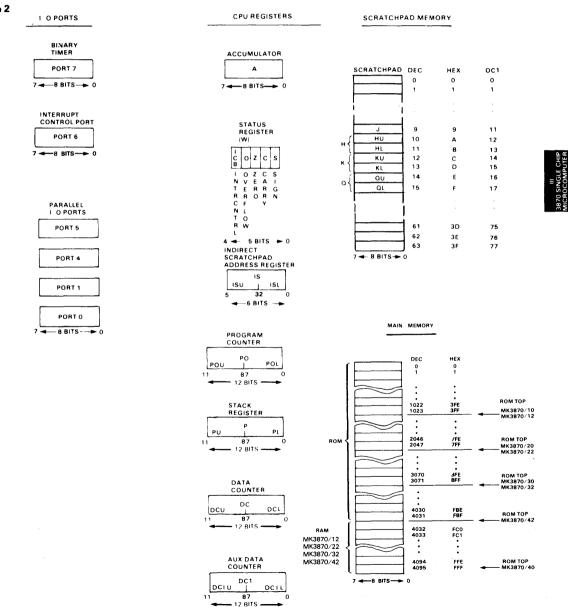

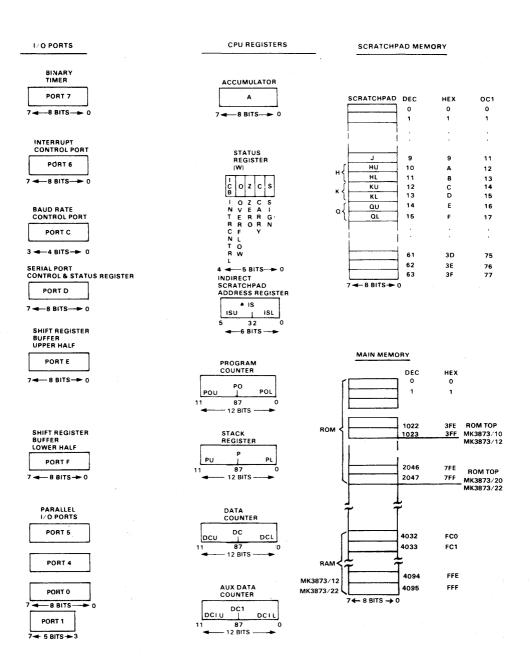

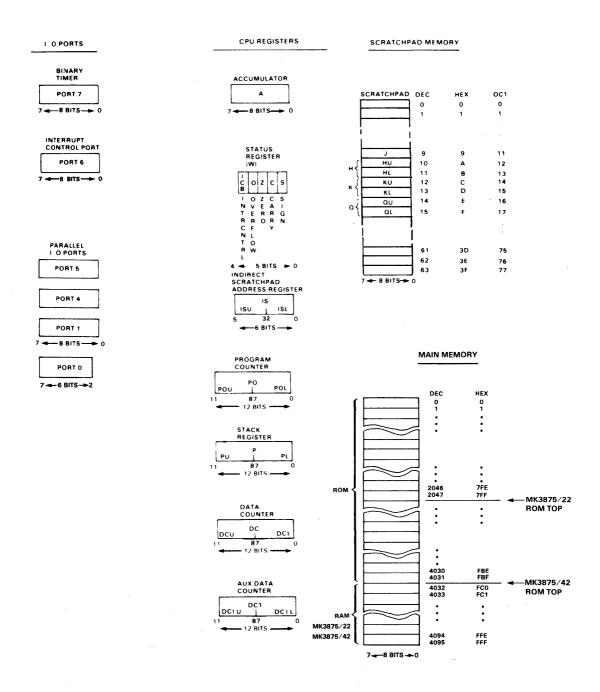

#### 3870 FAMILY PROGRAMMING MODEL Figure 4-3

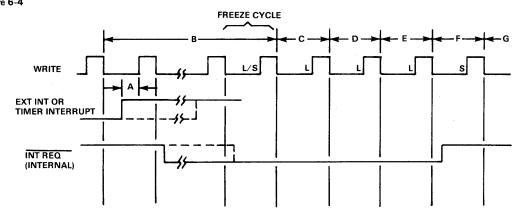

I/O PORTS **CPU REGISTERS** SCRATCHPAD MEMORY BINARY TIMER ACCUMULATOR PORT 7 А SCRATCHPAD DEC HEX 0C1 0 0 0 7 - 8 BITS - 0 - 8 BITS ---- 0 7 ◄ 1 1 1 INTERRUPT CONTROL PORT STATUS J 9 9 11 REGISTER PORT 6 HU 10 Α 12 (W) н HL в 13 11 0 Z С C B S С ĸυ 12 14 к D 15 KL 13 0 Z Ĉ T S Е N VEA Qυ 14 16 4 Q ERRG QL 15 F 17 RC RORN F ٧ PARALLEL N L I/O PORTS т 0 R w PORT 5 75 3D 61 L 62 ЗE 76 4 - 5 BITS - 0 ЗF 77 63 INDIRECT PORT 4 SCRATCHPAD 7 🗲 8 BITS 🔶 0 ADDRESS REGISTER IS PORT 1 ISU ISL 32 5 - 6 BITS - 0 PORT 0 7-- 8 BITS ----- 0 MAIN MEMORY PROGRAM COUNTER PO DEC HEX POU PÓL 0 0 87 1 1 11 🔫 - 12 BITS -- 0 1022 3FE ROM TOP STACK REGISTER 1023 3FF MK3870/10 MK3870/12 P ΡU PI 2046 7FE , 87 ROM ROM TOP 2047 7FF — 12 BITS — MK3870/20 11 🗲 - D MK3870/22 3070 8FE ROM TOP DATA 3071 8FF MK3870/30 COUNTER MK3870/32 DC DCU DCI 4030 FBE 87 4031 FBF ROM TOP 4032 FC0 MK3870/42 11 🗲 - 12 BITS ---- 0 ROM 4033 FC1 MK3870/12 MK3870/22 AUX DATA MK3870/32 4094 FFE ROM TOP COUNTER MK3870/42 4095 FFF MK3870/40 DC1 7 🗲 8 BITS -> 0 DCIU DCIL 87

11 - 12 BITS - 0

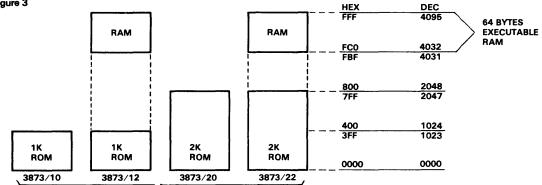

#### 4.6 MAIN MEMORY AND MAIN MEMORY ADDRESSING

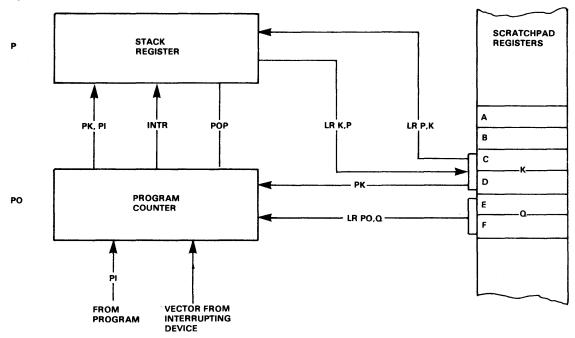

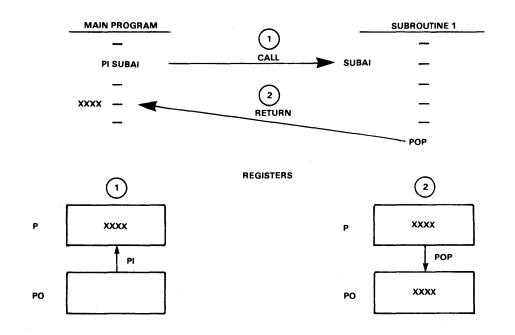

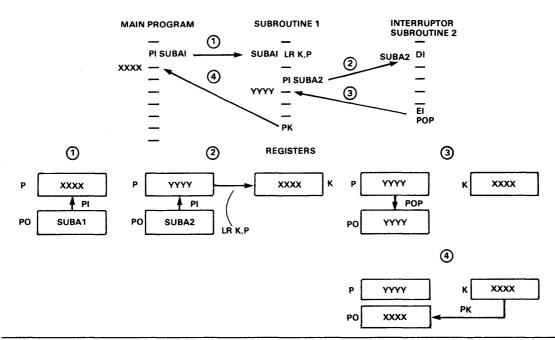

The Main Memory section of the 3870 consists of a combination of ROM and executable RAM. There are four registers associated with the Main Memory Array. These are the Program Counter (P0), the Stack Register (P), the Data Counter (DC) and the Auxiliary Data Counter (DC1). The Program Counter is used to address instructions during program execution. P is used to save the contents of P0 during an interrupt or subroutine call. Thus, P contains the return address at which processing is to resume upon completion of the subroutine or the interrupt routine.

The Data Counter (DC) is used to address data tables. This register is auto-incrementing. Of the two data counters only DC can access the ROM. However, the XDC instruction allows DC and DC1 to be exchanged.

Associated with the address registers is an Adder/Incrementer. This logic element is used to increment P0 or DC when required and is also used to add displacements to P0 on relative branches or to add the data bus contents to DC in the ADC (Add Data Counter) instruction.

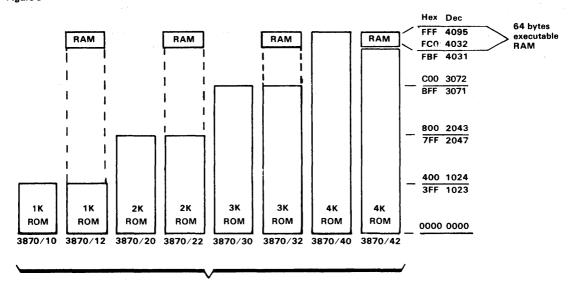

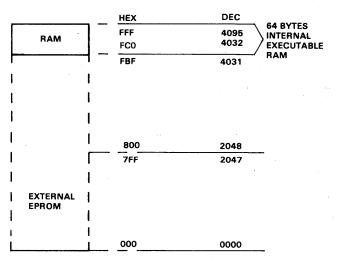

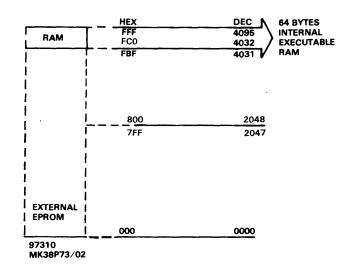

The amount of on chip ROM currently available on 3870 Family devices ranges from 0 bytes on P-PROM emulator parts to 4096 bytes on the MK3870/40. The microcomputer program and data constants may be stored in the program ROM. When a ROM access is required, the appropriate address register (P0 or DC) is gated onto the ROM address bus and the ROM ouput is gated onto the main data bus. On the P-PROM devices, external EPROM memeory is addressed and used as program memory since there is no on chip ROM on these devices.

Some 3870 single chip microcomputers, such as the MK3870/22, have RAM which is addressable in the main memory map in addition to the 64 bytes of scratchpad RAM which exists on all 3870 Family devices. This extra RAM can be used for additional storage of variables, or since it is addressed the same as program memory, it is conceivable that software routines can be loaded into this RAM memory and executed. It is for this reason that additional RAM on 3870 microcomputers is termed executable RAM.

#### 4.7 SCRATCHPAD AND IS

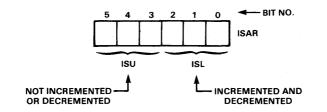

The scratchpad provides 64 8-bit registers which may be used as general purpose RAM memory. The Indirect Scratchpad Address Register (IS) is a 6 bit register used to address the 64 registers. All 64 registers may be accessed using IS. In addition, the lower order 12 registers may also be directly addressed.

IS can be visualized as holding two octal digits as illustrated in Figure 4-4. This visualization of IS is important since a number of instructions increment or decrement only the least significant 3 bits of IS when referencing scratchpad bytes via IS. This makes it easy to reference a buffer consisting of contiguous scratchpad bytes. For example, when the low order octal digit is incremented or decremented IS is incremented from octal 27 (0 '27') to 0 '20' or is decremented from 0 '20' to 0 '27'. (The notation O'nn' is used to specify an octal number.)

#### THE ISAR REGISTER Figure 4-4

This feature of the IS is very useful in many program sequences. All six bits of IS may be loaded at one time or either half may be loaded independently.

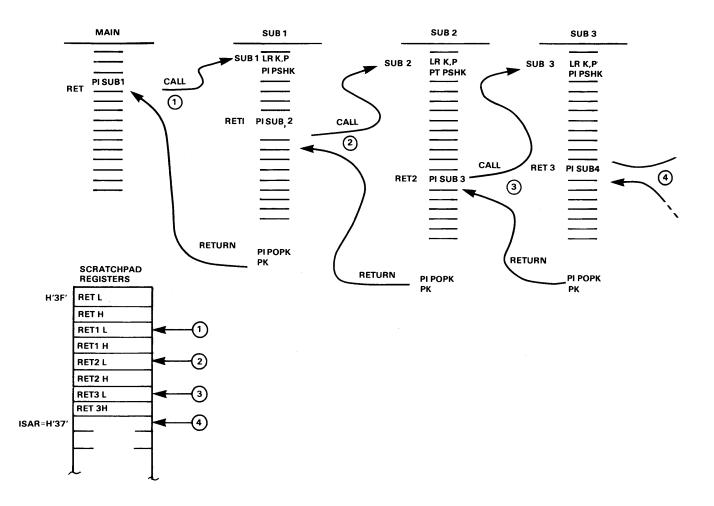

Scratchpad registers 9-15 (decimal) are given mnemonic names (J,H,K, and Q) because of special linkages between these registers and other registers such as the Stack Register. These special linkages facilitate the implementation of multi-level interrupts and subroutine nesting. For example, the instruction LR K,P stores the lower eight bits of the Stack Register into 13 (K lower or KL) and stores the upper three bits of P into register 12 (K upper or KU).

Figure 4-5 identifies the data transfers which may take place by executing a single 3870 instruction. For example, the illustration: W register  $\iff$  J means that a single instruction can move the contents of the W (or status) register to scratchpad register 9 (also called the J register). Another single instruction can move data in the opposite direction. Some linkages exist in only one direction, e.g. PO,  $\ll$  Q.

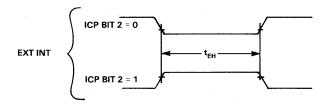

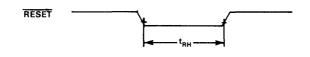

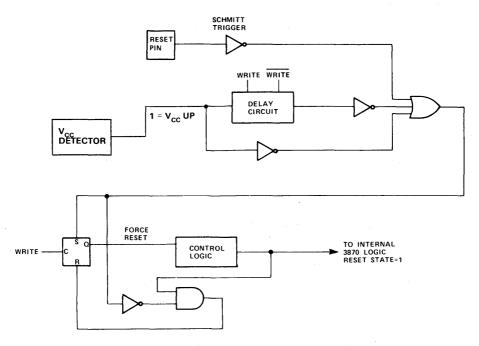

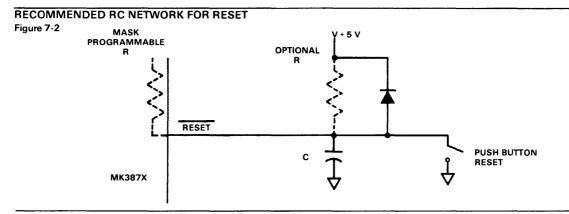

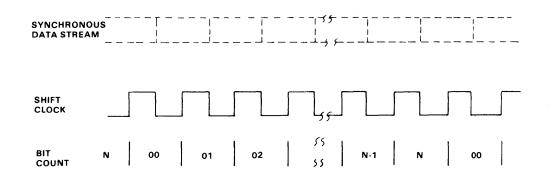

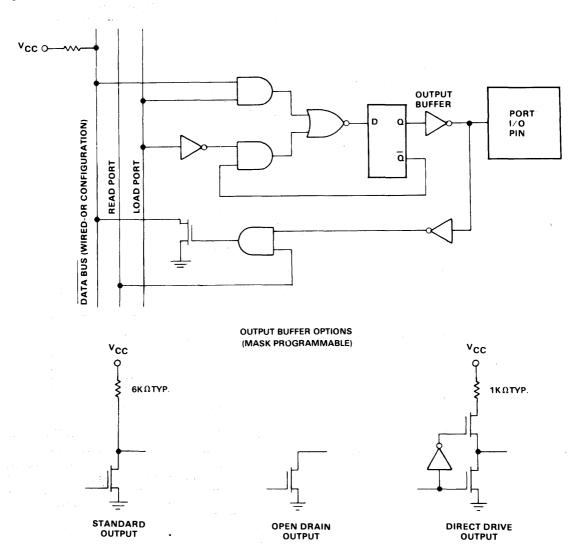

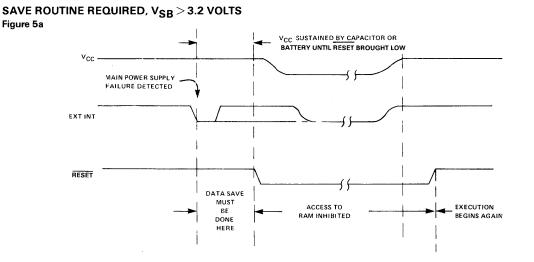

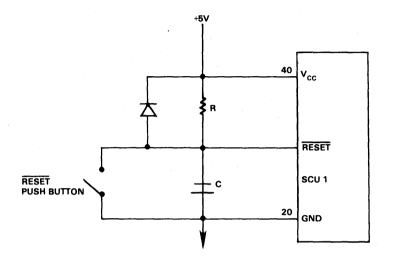

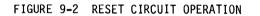

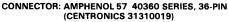

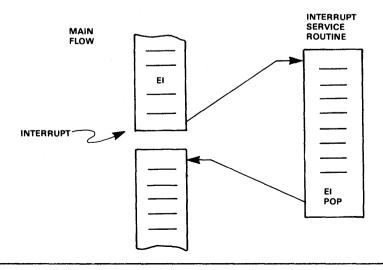

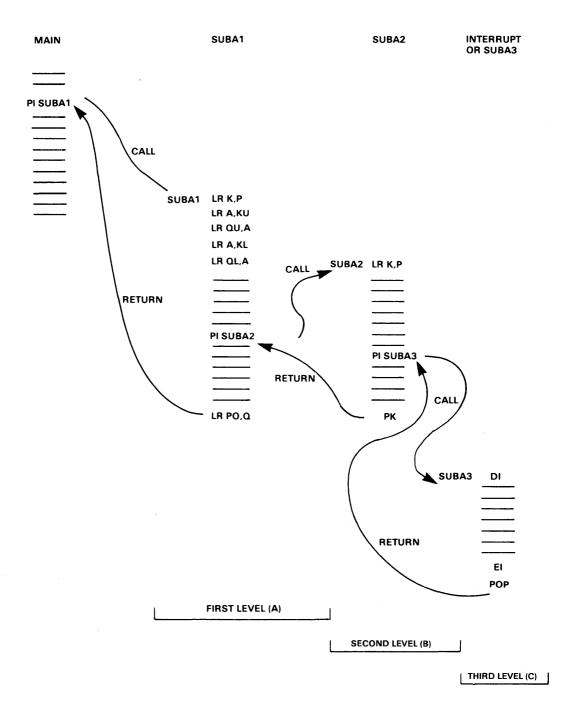

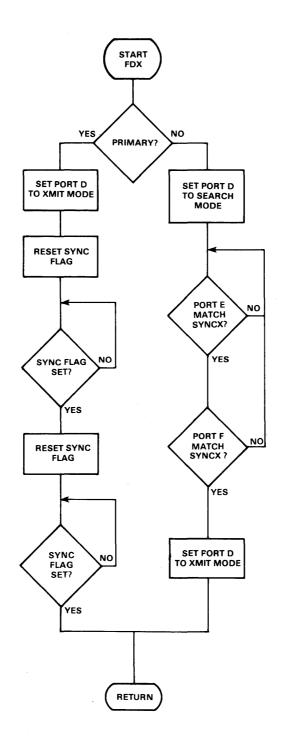

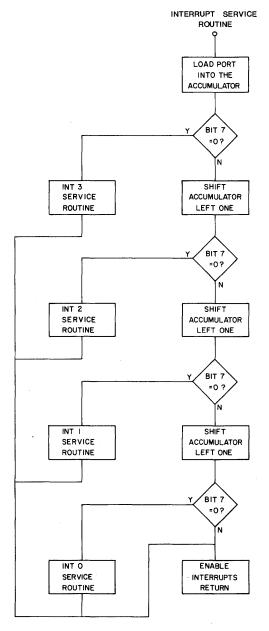

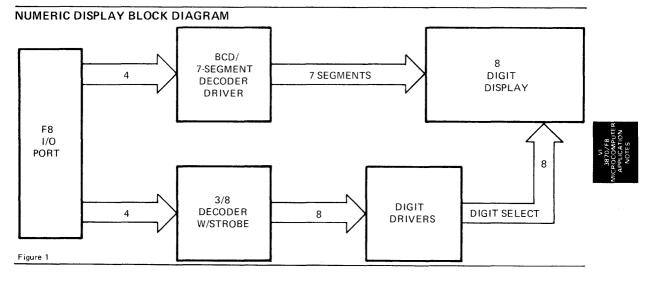

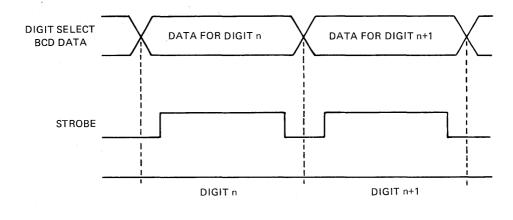

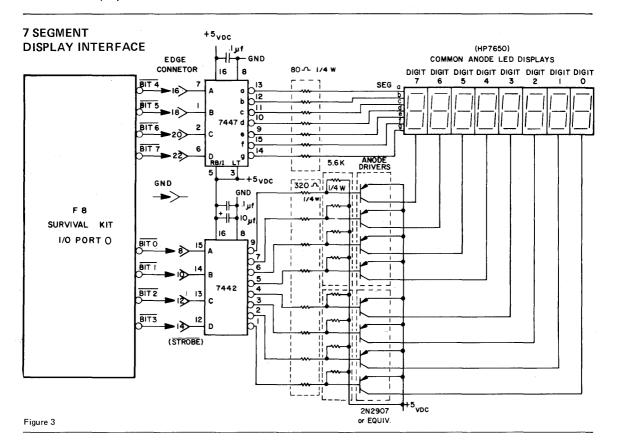

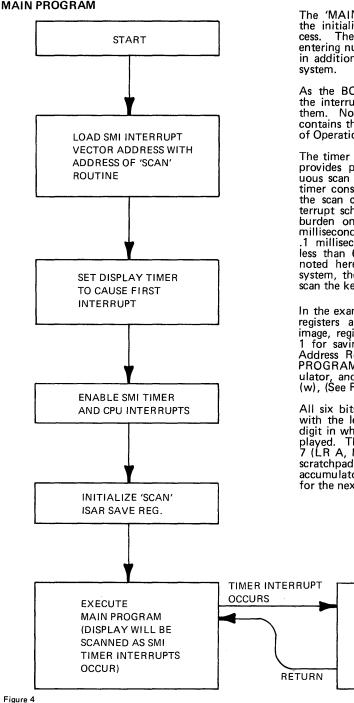

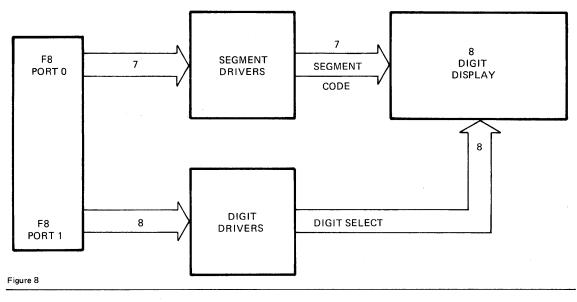

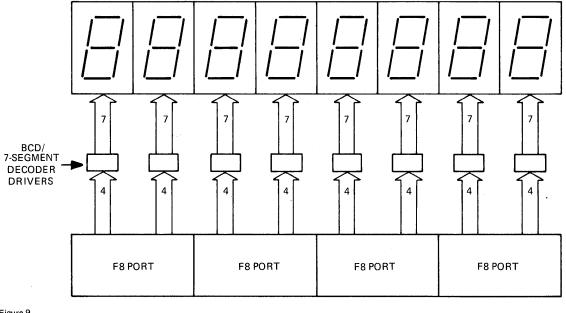

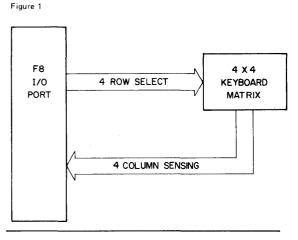

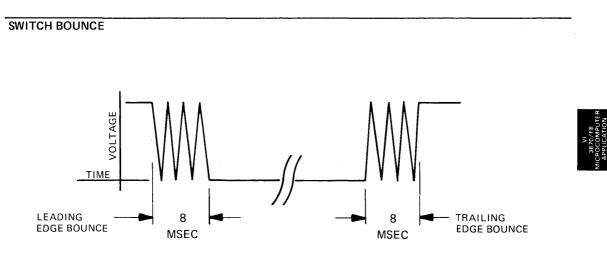

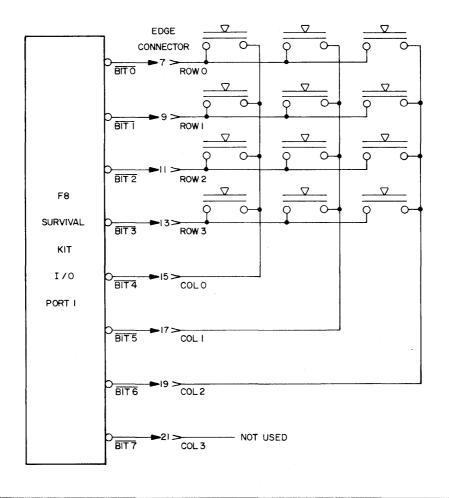

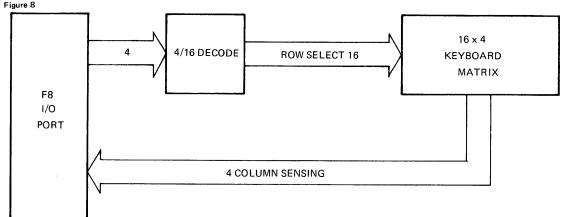

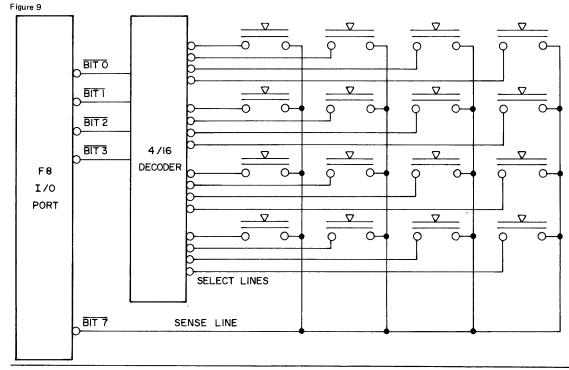

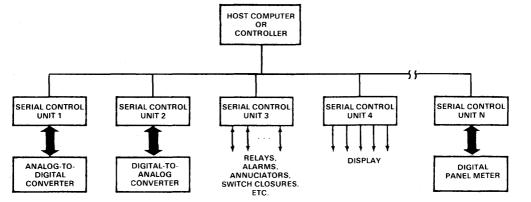

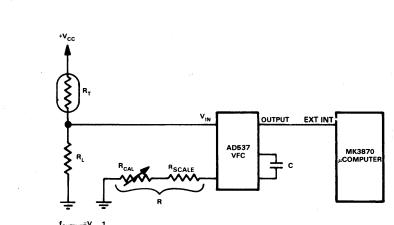

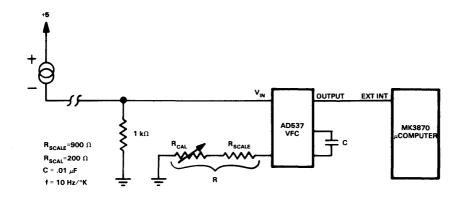

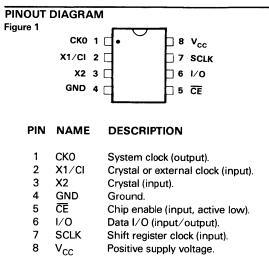

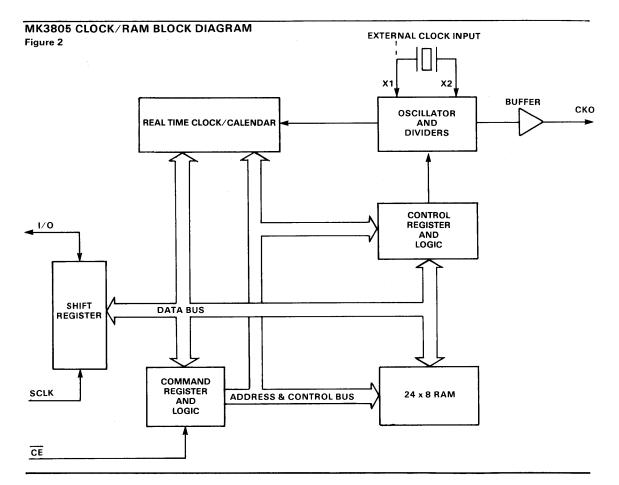

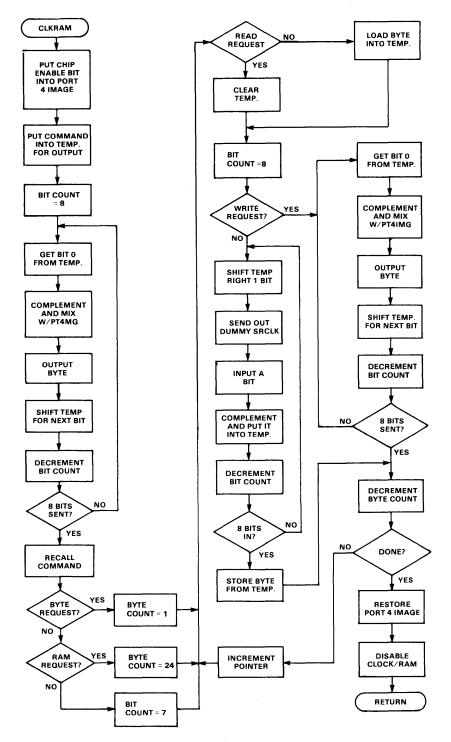

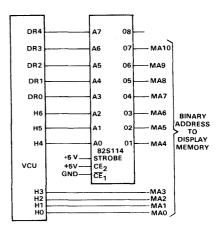

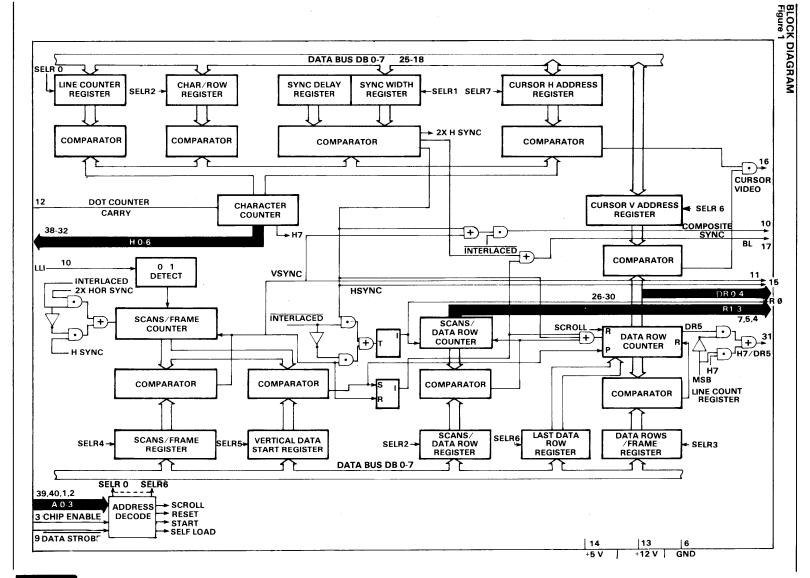

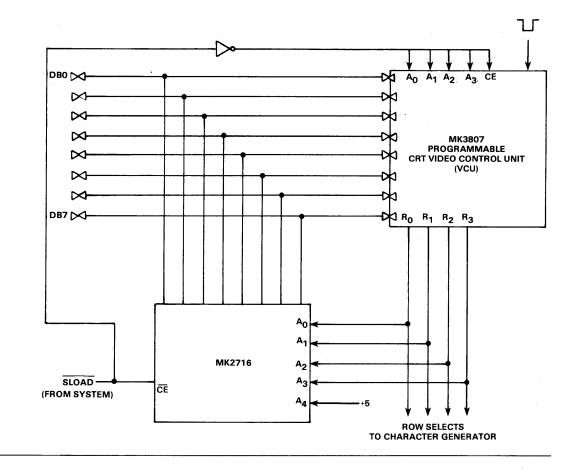

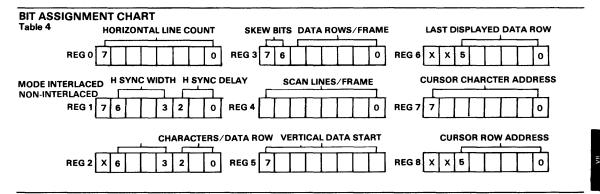

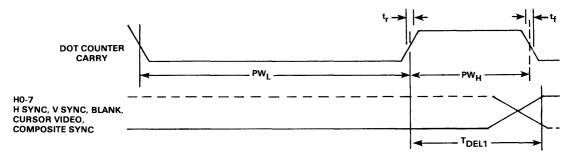

#### SCRATCHPAD REGISTER MAP Figure 4-5